## TI Designs

# 4-GHz Clock Reference Design for 12-Bit High-Speed ADCs in Digital Oscilloscopes and Wireless Testers

## **Description**

The TIDA-01015 is a clocking solution reference design for high-speed direct RF sampling GSPS ADCs. This TI Design showcases the significance of the sampling clock to achieve high SNR for second Nyquist zone input signal frequencies. The ADC12J4000 device is a 12-bit, 4-GSPS RF sampling ADC with a 3-dB input bandwidth of 3.2 GHz capable of capturing signals up to 4 GHz. This design highlights a clocking solution for the ADC12J4000 using TRF3765 to achieve high SNR performance at high input frequencies used in applications such as digital storage oscilloscopes (DSO) and wireless testers.

#### Resources

TIDA-01015 Design Folder

ADC12J4000EVM Tool Folder

ADC12J4000 Product Folder

TRF3765 Product Folder

LMK04828 Product Folder

TSW14J56EVM Tool Folder

ASK Our E2E Experts

#### **Features**

- 12-Bit, 4-GSPS RF Sampling ADC Clocking Solution

- Up to 4-GHz Input Signal Capture Capability

- JESD204B Compliant Low-Phase Noise Clocking Solution for RF Sampling ADC

#### **Applications**

- Oscilloscopes

- Wireless Communication Testers

- Phased Array Radar

- Software Defined Radio

A

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

System Overview www.ti.com

## 1 System Overview

### 1.1 System Description

RF sampling ADCs are capable of capturing and digitizing RF signals higher than the sampling frequency. A high-speed GSPS RF sampling ADC requires a low-noise clocking solution to achieve high SNR. This TI Design focuses on the clocking solution for high-speed GSPS ADCs used in applications such as DSO, wireless testers, radar, and so on. In this TI Design, the TRF3765 RF synthesizer is used as a sampling clock source for the ADC12J4000. The TRF3765 is capable of generating clock frequencies up to 4.8 GHz and the ADC12J4000 is a 12-bit, 4-GSPS wideband ADC.

In this solution, the TRF3765 receives a 100-MHz VCXO reference signal and generates the ADC12J4000's DEVCLK (sampling clock). The TRF3765 is also used after being divided to clock the LMK04828, which is in clock distribution mode to generate SYSREF for the ADC and other clocks required for the JESD204B interface between the ADC and the FPGA.

Oscilloscopes require a wide bandwidth analog front-end (AFE). The ADC12J4000 ADC is well suited for these requirements. The clocking solution described in this TI Design provides an optimum solution for clocking the ADC12J4000 to achieve wide bandwidth and high SNR.

Wireless tester equipment requires high dynamic range and wide receiver bandwidth for 3G and later wireless standards. The ADC12J4000 ADC is well suited for these requirements. The clocking solution described in this TI Design provides an optimum solution for clocking the ADC12J4000 to achieve both high dynamic range and wide receiver bandwidth for wireless tester applications.

A radar end application needs high dynamic range, wide receiver bandwidth, and low latency. The signal chain solution based on the ADC12J4000, TRF3765, and LMK04828 helps to achieve optimum performance for radar applications.

RF-sampling software defined radio (SDR) technology needs high dynamic range, highly re-configurable receiver bandwidth, and wide input frequency range. This TI Design can meet most of the requirements of the high-performance SDRs in terms of dynamic range and re-configurability.

### 1.2 Key System Specifications

The objective of this TI Design is to study the TRF3675-LMK04828 clocking solution performance when used in within an ADC12J4000 signal chain. The design focuses on achieving high SNR for input signal frequencies in the second Nyquist zone. The input balun and passives were modified to enhance the input frequency range up to 4 GHz. Table 1 lists the key system level specifications for the signal chain from the clocking solution perspective. SNR is specified after considering the impact of the balun and other elements in the ADC12J4000EVM.

**SPECIFICATIONS PARAMETER CONDITIONS** 55.0 350-MHz input signal 54.8 600-MHz input signal 52.0 900-MHz input signal Signal-to-noise ratio 51.2 1500-MHz input signal (SNR in dBFS) 48.7 2400-MHz input signal 48.5 2700-MHz input signal 45.0 3700-MHz input signal

Table 1. Key System Level Specifications

www.ti.com System Overview

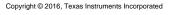

## 1.3 Block Diagram

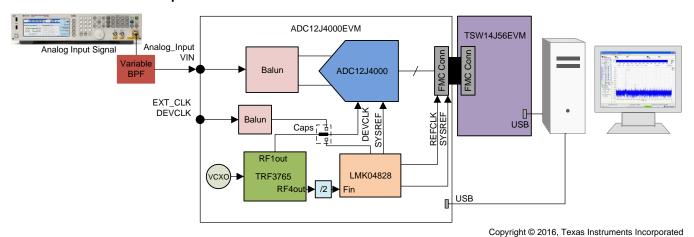

The block diagram of the clocking solution for ADC12J4000EVM and data capture using the TSW14J56EVM are shown in Figure 1. The ADC12J4000EVM signal chain contains a balun to convert the single-ended input signal to differential and is provided to the ADC inputs.

Copyright © 2016, Texas Instruments Incorporated

Figure 1. Block Diagram of ADC12J4000EVM and TSW14J56EVM Test Setup

## 1.4 Highlighted Products

#### 1.4.1 ADC12J4000

The ADC12J4000 is a wideband sampling high speed ADC with JESD204B interface. It includes a 12-bit, 4-GSPS ADC with integrated DDC with programmable NCO and decimation settings (including an undecimated 12-bit ADC output). It has a 3-dB input bandwidth of 3.2 GHz and is usable up to 3 GHz and beyond. The device input is buffered with an on-chip differential termination of 100  $\Omega$ .

#### 1.4.2 TRF3765

The TRF3765 is a wideband integer-N and Fractional-N frequency synthesizer with an integrated, wideband voltage-controlled oscillator (VCO). The TRF3765 can generate continuous frequency coverage from 300 MHz to 4.8 GHz using the programmable output dividers.

#### 1.4.3 LMK04828

The LMK04828 is a dual-PLL jitter cleaner and clock generator. The device receives a divided frequency from the TRF3765 and operates in clock distribution mode. The LMK04828 supplies the SYSREF clock to the ADC and other clocks for the JESD204B FPGA interface.

## 2 Getting Started Hardware and Software

#### 2.1 Hardware Configuration

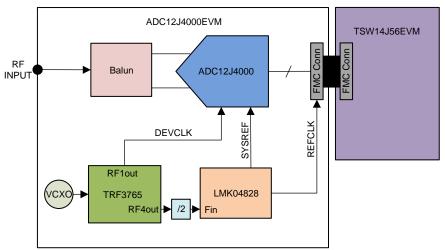

## 2.1.1 ADC12J4000EVM Setup

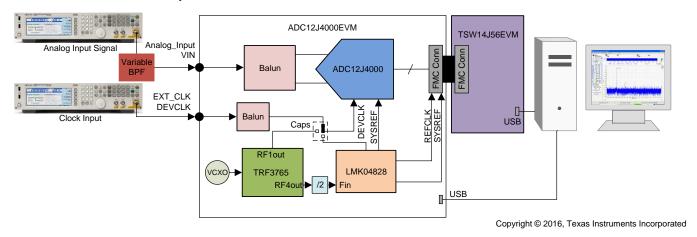

Figure 2 shows the block diagram for the setup of the ADC12J4000EVM. Follow the ADC12J4000EVM user's guide[1] (SLAU551) for the ADC12J4000EVM hardware setup procedure. The ADC12J4000EVM has both internal as well as external options for clocking the ADC. Selecting the DEVCLK is based on the placement of capacitors on the shared pads. In external clock mode, connect a signal generator set for 4 GHz to the external clock input (DEVCLK).

Copyright © 2016, Texas Instruments Incorporated

Figure 2. Block Diagram of ADC12J4000EVM

On the original EVM, the balun T1 supports an input frequency up to 3 GHz. In this TI Design, the balun was replaced with the BD2040J50100AHF to support frequencies up to 4 GHz.

#### 2.1.2 TSW14J56EVM Setup

Follow the TSW14J56EVM user's guide[2] (SLWU086) for the TSW14J56EVM hardware setup procedure.

## 2.2 Software Configuration

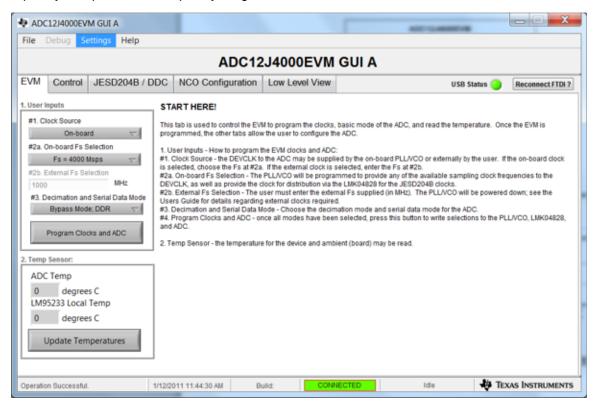

#### 2.2.1 ADC12J4000EVM Programming

Follow the ADC12J4000EVM user's guide[1] (SLAU551) to load the configuration files for ADC and clocks. The ADC12J4000EVM is put into bypass mode to use the full Nyquist zone of the device. The EVM is setup in onboard clock source selection mode, select a sampling frequency of 4000 Msps and click *Program Clocks and ADC*. Follow the ADC12J4000EVM user's guide for changing the onboard sampling frequency to a predefined frequency range.

Figure 3. ADC12J4000EVM Programming

#### 2.2.2 HSDC Pro Setup

The HSDC Pro software interfaces with the TSW14J56 to capture and analyze the digital data from the ADC12J4000. Follow the TSW14J56EVM user's guide[2] (SLWU086) for HSDC Pro setup and to capture and analyze the data.

Testing and Results www.ti.com

## 3 Testing and Results

## 3.1 Test Setup

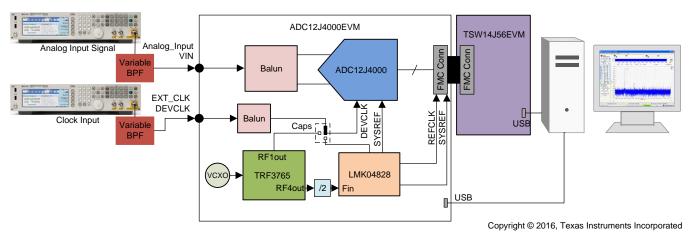

The ADC12J4000EVM connects to the TSW14J56EVM capture card, which is interfaced by HSDC Pro software to capture and analyze the data. A low-noise signal generator generates the required single-tone signal. A band-pass filter (BPF) suppresses the signal-generator harmonics. Balun T1 is replaced with the BD2040J50100AHF to enhance the input frequency range up to 4 GHz. In this TI Design, SNR measurements were performed at various frequencies with and without the clock BPF and measured results are tabulated in Section 3.2.

#### 3.1.1 Internal Clock Input

Figure 4. Test Setup for Internal Clock Signal

## 3.1.2 External Clock Input

Figure 5. Test Setup for External Clock Signal

www.ti.com Testing and Results

## 3.1.3 External Clock Input With BPF

Figure 6. Test Setup for External Clock Signal With BPF

#### 3.2 Results

Table 2 shows the measured SNR performance at various frequencies for a -1-dBFS differential input. The test results also show the SNR performance at the enhanced input frequency range around 4 GHz.

| INPUT FREQ<br>(MHz) | EXPECTED SNR (dBFS) | MEASURED SNR (dBFS)<br>(4-GHz EXTERNAL CLOCK) | MEASURED SNR (dBFS)<br>(4-GHz INTERNAL CLOCK, TRF3765) |

|---------------------|---------------------|-----------------------------------------------|--------------------------------------------------------|

| 350                 | 55.0                | 55.24                                         | 53.96                                                  |

| 600                 | 54.8                | 55.44                                         | 54.15                                                  |

| 900                 | 52.0                | 54.43                                         | 53.20                                                  |

| 1500                | 51.2                | 53.07                                         | 52.97                                                  |

| 2400                | 48.7                | 49.79                                         | 49.17                                                  |

| 2700                | 48.5                | 49.13                                         | 49.02                                                  |

| 3700                | 45.0                | 46.13                                         | 45.65                                                  |

**Table 2. Measured Results**

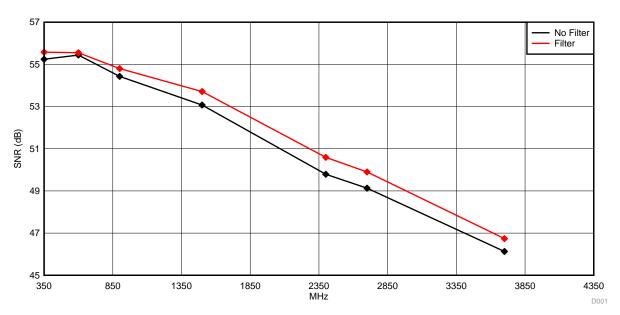

Table 3 shows the SNR improvement when the applied external clock signal is filtered and Figure 7 shows the SNR variation with and without clock filter. This test has been performed with the external clock input from a precision signal generator.

| INPUT FREQ<br>(MHz) | EXPECTED SNR (dBFS) | MEASURED SNR (dBFS)<br>(4-GHz EXTERNAL CLOCK) | MEASURED SNR (dBFS)<br>(4-GHz INTERNAL CLOCK, TRF3765) |

|---------------------|---------------------|-----------------------------------------------|--------------------------------------------------------|

|                     |                     | NO FILTER                                     | BPF at CLK                                             |

| 350                 | 55.0                | 55.24                                         | 55.58                                                  |

| 600                 | 54.8                | 55.44                                         | 55.55                                                  |

| 900                 | 52.0                | 54.43                                         | 54.80                                                  |

| 1500                | 51.2                | 53.07                                         | 53.71                                                  |

| 2400                | 48.7                | 49.79                                         | 50.59                                                  |

| 2700                | 48.5                | 49.13                                         | 49.90                                                  |

| 3700                | 45.0                | 46.13                                         | 46.74                                                  |

Table 3. Measured SNR Performance With and W/O Clock Filter

Testing and Results www.ti.com

Figure 7. Measured SNR With and Without Clock Filter

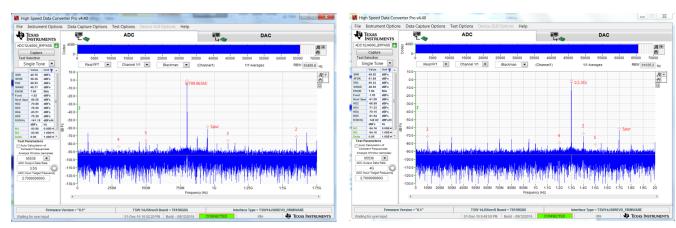

Further analysis shows the significance of different clock frequencies for the same input frequency. Figure 8 and Figure 9 show the spectral results for a 2700-MHz input signal at two different clock frequencies, 3.5 GHz and 4.0 GHz, which are both in the second Nyquist zone.

Figure 8. Spectrum at 3.5-GHz Clock for 2.7-GHz Input

Figure 9. Spectrum at 4-GHz Clock for 2.7-GHz Input

www.ti.com Testing and Results

As can be seen from the measured results, the SNR is better for the 4-GHz clock for the 2.7-GHz input. The performance improvement can be contributed to the reduced sampling attenuation effect at 4.0 GHz versus 3.5 GHz as shown in Figure 10.

Figure 10. Approximate Gain Plot at Different Clock Frequencies

## 3.3 Summary

The TIDA-01015 is a clocking solution reference design for high-speed direct RF sampling GSPS ADCs that can be used for digital oscilloscopes, wireless testers, software defined radios, or other high-speed communication and data acquisition systems. This TI Design compares signal chain performance of using TI's high performance clocking solutions versus an ideal clocking source. Results with and without a clocking BPF are also studied. Finally, the significance and possible SNR improvement of using higher clock frequencies for second Nyquist inputs are demonstrated.

Design Files www.ti.com

## 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01015.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01015.

## 4.3 PCB Layout Recommendations

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01015.

## 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01015.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01015.

## 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01015.

#### 5 Software Files

To download the software files, see the design files at TIDA-01015.

#### 6 Related Documentation

- 1. Texas Instruments, ADC12J4000EVM User's Guide (SLAU551)

- 2. Texas Instruments, TSW14J56 JESD204B High-Speed Data Capture and Pattern Generator Card, TSW14J56 User's Guide (SLWU086)

#### 6.1 Trademarks

All trademarks are the property of their respective owners.

## 7 About the Authors

AJEET PAL is a systems engineer at Texas Instruments where he is responsible for developing reference design solutions for the Test and Measurement sector. Ajeet has six years of experience in RF and wireless subsystem design for cellular and wireless systems. Ajeet earned his bachelor of engineering in electronics and communication engineering from the Institute of Technology & Management (ITM) University at Gwalior and his master of technology in RF and microwave engineering from the Indian Institute of Technology (IIT) Kharagpur, India.

**SANKAR SADASIVAM** is a system architect in the Industrial Systems Engineering team at Texas Instruments where he is responsible for architecting and developing reference design solutions for the industrial systems with a focus on Test and Measurement. Sankar brings to this role his extensive experience in analog, RF, wireless, signal processing, high-speed digital, and power electronics. Sankar earned his master of science (MS) in electrical engineering from the Indian Institute of Technology, Madras.

#### IMPORTANT NOTICE FOR TI REFERENCE DESIGNS

Texas Instruments Incorporated ('TI") reference designs are solely intended to assist designers ("Designer(s)") who are developing systems that incorporate TI products. TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.

Tl's provision of reference designs and any other technical, applications or design advice, quality characterization, reliability data or other information or services does not expand or otherwise alter Tl's applicable published warranties or warranty disclaimers for Tl products, and no additional obligations or liabilities arise from Tl providing such reference designs or other items.

TI reserves the right to make corrections, enhancements, improvements and other changes to its reference designs and other items.

Designer understands and agrees that Designer remains responsible for using its independent analysis, evaluation and judgment in designing Designer's systems and products, and has full and exclusive responsibility to assure the safety of its products and compliance of its products (and of all TI products used in or for such Designer's products) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to its applications, it has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any systems that include TI products, Designer will thoroughly test such systems and the functionality of such TI products as used in such systems. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equipment includes, without limitation, all medical devices identified by the U.S. Food and Drug Administration as Class III devices and equivalent classifications outside the U.S.

Designers are authorized to use, copy and modify any individual TI reference design only in connection with the development of end products that include the TI product(s) identified in that reference design. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of the reference design or other items described above may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS AND OTHER ITEMS DESCRIBED ABOVE ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNERS AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS AS DESCRIBED IN A TI REFERENCE DESIGN OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Tl's standard terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products. Additional terms may apply to the use or sale of other types of TI products and services.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's non-compliance with the terms and provisions of this Notice.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated