# Migrating From MSP430F541x and MSP430F543x MCUs to MSP430F541xA and MSP430F543xA MCUs

Miguel Morales MSP430 Applications

#### **ABSTRACT**

This application report helps you migrate an application based on an MSP430F541x or MSP430F543x microcontroller (MCU) to an MSP430F541xA or MSP430F543xA MCU. This application report describes the main differences between the two device families and provides migration solutions for both software and hardware.

#### Contents

Device Comparison.....

| 2 | пагим  | /are Considerations                             |   |

|---|--------|-------------------------------------------------|---|

|   | 2.1    | PMM Settings and Low Power Consumption          | 2 |

|   | 2.2    | Operating Frequency vs Supply Voltage           | 3 |

|   | 2.3    | Internal Voltage Reference                      | 4 |

|   | 2.4    | Unified Clock System (UCS) Settings             | 4 |

|   | 2.5    | Cyclic Redundancy Check Module                  | 4 |

|   | 2.6    | Device Errata                                   | 4 |

| 3 | Firmwa | are Considerations                              |   |

|   | 3.1    | PMM Default States                              |   |

|   | 3.2    | Internal Voltage Reference                      |   |

|   | 3.3    | Bootloader (BSL)                                |   |

| 4 | Refere | ences                                           | 8 |

|   |        | List of Figure 2                                |   |

|   |        | List of Figures                                 |   |

| 1 | Freque | ency vs Supply Voltage for F543x                | 3 |

| 2 | Freque | ency vs Supply Voltage for F543xA               | 3 |

| 3 | PMMC   | CTL0 Register                                   | 5 |

| 4 | SVSM   | HCTL Register                                   | 5 |

| 5 | SVSM   | LCTL Register                                   | 6 |

| 6 |        | RIE Register                                    |   |

| 7 |        | TL0 Register                                    |   |

| 8 | Typica | al Temperature Sensor Transfer Function         | 7 |

|   |        | List of Tables                                  |   |

|   |        |                                                 |   |

| 1 |        | Level Differences Between F543x and F543xA MCUs |   |

| 2 | REFM   | STR Bit Description                             | 7 |

|   |        |                                                 |   |

# **Trademarks**

1

MSP430 is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

Device Comparison www.ti.com

### **Device Comparison**

The A revisions of the MSP430F541x and MSP430F543x microcontrollers (MCUs) offer better performance, lower power, and the full set of features for the MSP430F5xx MCUs. This enables a more robust and cost-optimized system design. Table 1 shows a general high-level comparison of the MCUs to provide an overview of reasons to consider migrating.

NOTE: In this migration guide, the term F543x is indicates the MSP430F541x and MSP430F543x MCUs (also known as the "non-A" versions), and the term F543xA indicates the MSP430F541xA and MSP430F543xA MCUs (also knowns as the "A" versions).

Table 1. High-Level Differences Between F543x and F543xA MCUs

|                                          | MSP430F541x and MSP430F543x       | MSP430F541xA and MSP430F543xA                                    |

|------------------------------------------|-----------------------------------|------------------------------------------------------------------|

| Maximum CPU clock speed                  | 18 MHz                            | 25 MHz                                                           |

| V <sub>CC</sub> operating range          | 2.2 V to 3.6 V                    | 1.8 V to 3.6 V                                                   |

| Standby current consumption (LPM3)       | 2.7 μΑ                            | 1.9 μA <sup>(1)</sup>                                            |

| Minimum voltage for flash ISP            | 2.2 V                             | 1.8 V                                                            |

| Bootstrap loader                         | Non-customizable                  | Customizable peripheral interface                                |

| Reliable operating temperature range (2) | -20°C to 85°C                     | -40°C to 85°C                                                    |

| ADC12 voltage reference                  | Internal 1.5-V or 2.5-V reference | General-purpose REF module<br>(1.5-V, 2.0-V, or 2.5-V reference) |

| LPM4.5 exit                              | LPM4.5 not supported              | Exit LPM4.5 using RST and/or port interrupts                     |

The value shown here is the expected current consumption and has not been characterized.

#### 2 **Hardware Considerations**

Fortunately, the F543xA versions of silicon have very few differences from the F543x versions that affect an application's hardware design. The package and pinout of the A versions is pin-to-pin compatible with the F543x versions.

#### 2.1 PMM Settings and Low Power Consumption

The FLASH28 erratum for the F543x MCUs reports read disturb problems when the Power Management Module (PMM) V<sub>CORE</sub> levels are <2 (PMMCOREVx = 10b). This limitation makes it necessary for the device V<sub>CORE</sub> be initialized to level 2 in the boot code, which is different from the expected default values of level 0 specified in the MSP430F5xx and MSP430F6xx Family User's Guide. The higher voltage applied to the core increases the power consumption in active and low-power modes. To prevent a condition in which the read-disturb problem negatively affects the application flow, the user should not lower the V<sub>core</sub> level in attempts to obtain lower power consumption.

The F543xA can operate at all PMM levels, allowing for even lower current consumption than its predecessor. For example, in LFXT1 standby mode (LPM3 using a 32-kHz watch crystal), the standby current consumption of an F543xA MCU is approximately 1.9 μA, compared to approximately 2.7 μA for an F543x MCU. This is a considerable advantage for applications that spend the majority of their time in standby mode.

LPM4.5 support has been added to the F543xA. LPM4.5 is equivalent to LPM4, except that the internal voltage regulator is disabled. All CPU operations, clocks, and peripherals are disabled in LPM4.5. LPM4.5 can be leveraged like LPM4 in previous MSP430™ MCUs, because it achieves the lowest power consumption and is intended for shelf-life applications or applications that must sit in the lowest-power mode for very long periods of time without any peripheral activity. The contents of RAM are cleared (including all peripheral initializations) when entering LPM4.5, and the device must trigger a BOR to wake into an active mode. This BOR can be triggered by the removal of power, by using the RST line, or through the use of a port interrupt. The ability to use port interrupts adds flexibility to the hardware design in that more than one pin is available for wakeup from LPM4.5 so external hardware resources can wake the device.

See erratum PMM6 in the device-specific erratasheet.

www.ti.com Hardware Considerations

# 2.2 Operating Frequency vs Supply Voltage

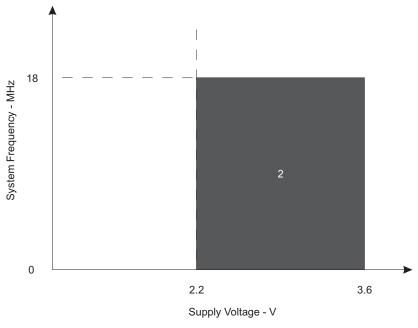

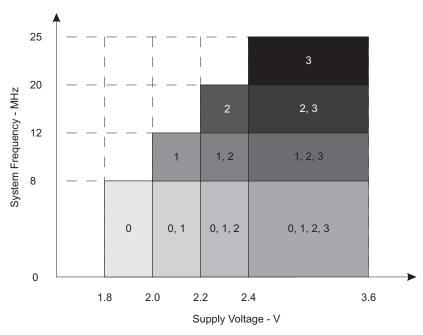

Figure 1 and Figure 2 show the frequency vs supply voltage curves for theF543x and F543xA MCUs, respectively.[1][2]

The numbers within the fields denote the supported PMMCOREVx settings.

Figure 1. Frequency vs Supply Voltage for F543x

The numbers within the fields denote the supported PMMCOREVx settings.

Figure 2. Frequency vs Supply Voltage for F543xA

Hardware Considerations www.ti.com

The limitation that an F543x MCU must operate at no less than PMMCOREVx level 2 makes the operating range 2.2 V to 3.6 V. Because in-system programming (ISP) for the flash memory is valid over the entire operating range for the device, this also limits the range for flash ISP procedures. Furthermore, the F543x MCUs are specified to run up to 18 MHz.

The F543xA MCUs can operate from 1.8 V to 3.6 V with valid flash ISP across the entire operating range (see Figure 2). F543xA MCUs can run at up to 25 MHz. This flexibility provides both the performance to execute highly CPU-intensive tasks as well as the ability to optimize power consumption according to the speed requirements of the application.

# 2.3 Internal Voltage Reference

One significant difference in the architecture of the F543xA MCUs is the replacement of the internal 1.5-V or 2.5-V reference (se the ADC12 block diagram in the MSP430F5xx and MSP430F6xx Family User's Guide) with a separate, general-purpose REF module that can provide voltages to the various analog peripherals on a given F5xx MCU. The implications to the application can be minimal, as the F543xA REF module includes a setting that is backward compatible with the F543x revisions of silicon (see Section 3 for details on enabling this mode). For the purpose of future compatibility, TI recommends using the REF module as a separate module and not in a backward-compatible mode.

At a high level, the improved features that the REF module provides are:

- Centralized trimmed bandgap with excellent PSRR, temperature coefficient, and initial accuracy

- 1.5-V, 2.0-V, and 2.5-V user selectable internal references

- Buffered bandgap voltage available to rest of system

- · Power saving features

- · Backward compatibility to existing reference system

For details on how to use the REF module, see the MSP430F5xx and MSP430F6xx Family User's Guide.

# 2.4 Unified Clock System (UCS) Settings

The logic for the Unified Clock System (UCS) has changed slightly for A revisions of silicon. The changes generally affect the conditions under which the four available reference oscillators, the reference oscillator (REFO), the very low frequency oscillator (VLO), and the two crystal oscillators (XT1 and XT2) are enabled or disabled. These differences are outlined extensively in the UCS chapter of the MSP430F5xx and MSP430F6xx Family User's Guide and should be reviewed for possible optimizations to the UCS configuration and overall power consumption. Existing UCS code should require no modification for proper execution.

#### 2.5 Cyclic Redundancy Check Module

A revisions of F543x silicon add two 'reverse' registers to the Cyclic Redundancy Check (CRC) module: a CRC Data In Reverse Byte (CRCDIRB) register and a CRC Result Reverse register. Data bytes written to CRCDIRB in word mode or the data byte in byte mode are bit-wise reversed before the CRC module adds them to the signature. The bits are reversed in order to enable the MSB bits to be shifted in first to the linear feedback shift register (LFSR) that composes the CRC machine. Similarly, the CRC Result Reverse register provides the byte results of the CRC in bit-wise reversed format.

# 2.6 Device Errata

In the course of migrating an existing application to the F543xA, it is recommended that the user review and carefully consider the latest device errata sheets to ensure the application is not affected by a known issue. Furthermore, the errata sheets typically outline workarounds along with the bug descriptions. Large improvements in the errata have been made for the A revisions of silicon that should be taken into account when migrating existing applications. For all MSP430 products, the device errata sheets can be found in the product folders of each product on the MSP430 web page.

www.ti.com Firmware Considerations

#### 3 Firmware Considerations

This section outlines important steps to consider when transitioning an existing application to an F543xA MCU. In general, an application should be rebuilt on a source-code level using the appropriate header and linker command files. This is the first step towards a successful migration to an A MCU. The following sections provide more details regarding key considerations that should be made for a successful port of the application.

#### 3.1 PMM Default States

#### 3.1.1 PMM Defaults for F543x

The default state of the following MSP430F541x and MSP430F543x PMM registers are not the default levels shown in the MSP430F5xx and MSP430F6xx Family User's Guide.

# 3.1.1.1 Power Management Module Control Register 0 (PMMCTL0)

Figure 3. PMMCTL0 Register

| 15       | 14       | 13   | 12        | 11       | 10       | 9      | 8      |  |  |

|----------|----------|------|-----------|----------|----------|--------|--------|--|--|

| PMMPW    |          |      |           |          |          |        |        |  |  |

| rw-1     | rw-0     | rw-0 | rw-1      | rw-0     | rw-1     | rw-1   | rw-0   |  |  |

| 7        | 6        | 5    | 4         | 3        | 2        | 1      | 0      |  |  |

| Reserved | Reserved |      | PMMREGOFF | PMMSWPOR | PMMSWBOR | PMMC   | COREV  |  |  |

| rw-0     | r-0      | r-0  | rw-0      | rw-0     | rw-0     | rw-[0] | rw-[0] |  |  |

**Default level:** PMMCTL0\_L = 0x00 (where '\_L' signifies the low byte of the register)

Actual level: PMMCTL0\_L = 0x02

The PMMCOREVx bits are set to level 2 in accordance with the FLASH28 erratum.

# 3.1.1.2 Supply Voltage Supervisor and Monitor High-Side Control Register (SVSMHCTL)

Figure 4. SVSMHCTL Register

| 15       | 14       | 13       | 12       | 11         | 10     | 9        | 8      |

|----------|----------|----------|----------|------------|--------|----------|--------|

| SVMHFP   | SVMHE    | Reserved | SVMHOVPE | SVSHFP     | SVSHE  | SVSH     | IRVL   |

| rw-[0]   | rw-1     | r-0      | rw-[0]   | rw-[0]     | rw-1   | rw-[0]   | rw-[0] |

| 7        | 6        | 5        | 4        | 3          | 2      | 1        | 0      |

| SVSMHACE | SVSMHEVM | Reserved | SVSHMD   | SVSMHDLYST |        | SVSMHRRL |        |

| rw-[0]   | rw-0     | r-0      | rw-0     | r-0        | rw-[0] | rw-[0]   | rw-[0] |

**Default level:** SVSMHCTL = 0x4400 **Actual level:** SVSMHCTL = 0x4602

To monitor operation at the proper  $V_{CC}$  voltage in accordance to the PMMCOREVx level 2, the SVS and SVM high-side levels are both set to level 2. Note that the default state of the SVS and SVM high-side modules is ON (SVMHE = SVSHE = 1).

Firmware Considerations www.ti.com

# 3.1.1.3 Supply Voltage Supervisor and Monitor Low-Side Control Register (SVSMLCTL)

Figure 5. SVSMLCTL Register

| 15       | 14       | 13       | 12       | 11         | 10     | 9        | 8      |

|----------|----------|----------|----------|------------|--------|----------|--------|

| SVMLFP   | SVMLE    | Reserved | SVMLOVPE | SVSLFP     | SVSLE  | SVSL     | RVL    |

| rw-[0]   | rw-1     | r-0      | rw-[0]   | rw-[0]     | rw-1   | rw-[0]   | rw-[0] |

| 7        | 6        | 5        | 4        | 3          | 2      | 1        | 0      |

| SVSMLACE | SVSMLEVM | Reserved | SVSLMD   | SVSMLDLYST |        | SVSMLRRL |        |

| rw-[0]   | rw-0     | r-0      | rw-0     | r-0        | rw-[0] | rw-[0]   | rw-[0] |

**Default level:** SVSMLCTL = 0x4400 **Actual level:** SVSMLCTL = 0x4602

To monitor  $V_{CORE}$  at the proper voltage in accordance to the PMMCOREVx level 2, the SVS and SVM low-side levels are both set to level 2. Note that the default state of the SVS and SVM low-side modules is ON (SVMLE = SVSLE = 1).

# 3.1.1.4 Power Management Module Reset and Interrupt Enable Register (PMMRIE)

Figure 6. PMMRIE Register

| 15       | 14        | 13        | 12         | 11       | 10        | 9         | 8          |

|----------|-----------|-----------|------------|----------|-----------|-----------|------------|

| Reserved |           | SVMHVLRPE | SVSHPE     | Rese     | erved     | SVMLVLRPE | SVSLPE     |

| r-0      | r-0       | rw-[0]    | rw-[1]     | r-0      | r-0       | rw-[0]    | rw-[1]     |

| 7        | 6         | 5         | 4          | 3        | 2         | 1         | 0          |

| Reserved | SVMHVLRIE | SVMHIE    | SVSMHDLYIE | Reserved | SVMLVLRIE | SVMLIE    | SVSMLDLYIE |

| r-0      | rw-0      | rw-0      | rw-0       | r-0      | rw-0      | rw-0      | rw-0       |

**Default level:** PMMRIE = 0x0000 **Actual level:** PMMRIE = 0x1100

In accordance with erratum PMM7, the SVS low-side and SVS high-side POR enable bits (SVSLPE and SVSHPE) in PMMRIE are set by default such that the SVS will be configured to trigger a POR signal in the condition that the monitored voltages fall below the SVS levels.

#### 3.1.2 PMM Defaults for F543xA

The PMM levels on the F543xA are all set to the default levels specified in the user's guide. This has an important implication on the application. The default PMMCOREVx level of 0, for example, limits the maximum DCO speed to 8 MHz. To operate at higher frequencies, the application must first increase the  $V_{\text{CORE}}$  voltage and the respective SVS and SVM settings during initialization procedures.

NOTE: The procedure to increment the PMMCOREVx and SVS/SVM levels requires specific steps, documented in the PMM chapter of the MSP430F5xx and MSP430F6xx Family User's Guide. The files msp430x54xA\_PMM.h and msp430x54xA\_PMM.c in the MSP430F543xA code examples implement this procedure in the SetVCore(level) function. This function should be used to increment or decrement the PMMCOREVx levels.

www.ti.com Firmware Considerations

# 3.2 Internal Voltage Reference

Figure 7 shows the REF module control register. The REF module is used to source the internal voltage references of the ADC12\_A and other analog peripherals in a modular fashion with improved flexibility and stability. The simplest way to port an application that uses the ADC12 module is to set REFMSTR = 0 when initializing the ADC12 registers and to account for the increase in settling time for the internal reference, from 35  $\mu$ s to 75  $\mu$ s. The REF module is recommended to be used as the internal reference:

REFCTLO &= ~REFMSTR;

#### **Table 2. REFMSTR Bit Description**

| Bit | Field   | Туре | Reset | Description                                                                                                                |

|-----|---------|------|-------|----------------------------------------------------------------------------------------------------------------------------|

| 7   | REFMSTR | RW   | 1h    | REF master control. ADC10_A and CTSD16 devices: Must be written 1.                                                         |

|     |         |      |       | 0b = Reference system controlled by legacy control bits inside the ADC12_A module when available.                          |

|     |         |      |       | 1b = Reference system controlled by REFCTL register. Common settings inside the ADC12_A module (if exists) are don't care. |

#### Figure 7. REFCTL0 Register

|         |          |        | _      | _        |            |          |           |

|---------|----------|--------|--------|----------|------------|----------|-----------|

| 15      | 14       | 13     | 12     | 11       | 10         | 9        | 8         |

|         | Rese     | erved  |        | BGMODE   | REFGENBUSY | REFBGACT | REFGENACT |

| r0      | rO       | r0     | rO     | r-(0)    | r-(0)      | r-(0)    | r-(0)     |

| 7       | 6        | 5      | 4      | 3        | 2          | 1        | 0         |

| REFMSTR | Reserved | REF    | VSEL   | REFTCOFF | Reserved   | REFOUT   | REFON     |

| rw-(1)  | r0       | rw-(0) | rw-(0) | rw-(0)   | r0         | rw-(0)   | rw-(0)    |

Can be modified only when REFGENBUSY = 0.

For information on using the REF module, see the MSP430F5xx and MSP430F6xx Family User's Guide.

#### 3.2.1 ADC12 Temperature Sensor Equation

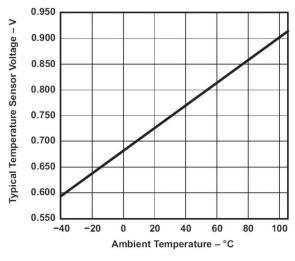

There is an on-chip temperature sensor available on the analog input channel 10. The result of sampling the temperature sensor is translated to a temperature value by applying a transfer function, shown in Figure 8.

Figure 8. Typical Temperature Sensor Transfer Function

This transfer function has two key parameters that are used to calculate the Temperature in degrees Celsius,  $TC_{SENSOR}$  and  $V_{SENSOR}$  (see Equation 1).

$$V_{SENSE} = TC_{SENSOR} \times (Temperature, C) + V_{SENSOR}$$

(1)

Firmware Considerations www.ti.com

The typical values for  $TC_{SENSOR}$  and  $V_{SENSOR}$  are specified in the section 12-bit ADC, Temperature Sensor and Built-In VMID of the data sheet. It is important to note that these values differ between the F543x and the F543xA, and this difference should be accounted for in the application.

### 3.3 Bootloader (BSL)

The SYS4 erratum, fixed in the A revisions, states that the BSL is non-programmable. Read disturb issues when executing code from non-Main memory segments of Flash were worked around in the current BSL using carefully aligned instructions, forcing it to be locked from user edit. These read disturb issues do not affect A revisions of silicon; therefore, the peripheral interface to the BSL is now user-programmable. See the MSP430<sup>TM</sup> Flash Devices Bootloader (BSL) User's Guide for further information concerning how to program the peripheral interface of the BSL.

#### 4 References

- 1. MSP430F543x, MSP430F541x Mixed-Signal Microcontrollers data sheet

- 2. MSP430F543xA, MSP430F541xA Mixed-Signal Microcontrollers data sheet

- 3. Migrating From MSP430F16x MCUs to MSP430F261x MCUs

- 4. MSP430F5xx and MSP430F6xx Family User's Guide

www.ti.com Revision History

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | Changes from April 16, 2010 to April 1, 2019 |     |  |  |  |  |  |

|----|----------------------------------------------|-----|--|--|--|--|--|

| •  | Editorial changes throughout document        | . 1 |  |  |  |  |  |

| •  | Removed broken hyperlink in Table 1          | . 2 |  |  |  |  |  |

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated