# POWERLINK on TI Sitara<sup>™</sup> Processors

**TEXAS INSTRUMENTS**

**Frank Walzer** Senior Systems Engineer Texas Instruments

# **Overview**

POWERLINK is a real-time Ethernet fieldbus system based on Ethernet standard IEEE 802.3. It was initially developed by B&R and was introduced in 2001. Since 2003, further development is driven by the Ethernet POWERLINK Standardization Group (EPSG), an independent user organization. The EPSG cooperates with other relevant standardization and user organizations such as CiA or IEC. Free open-source versions of POWERLINK have been available since 2008.

POWERLINK supports Ethernet standard features such as cross-traffic, hot-plugging and different types of network configurations such as star, ring and mixed topologies.

The communication profile of Ethernet POWERLINK is based on CANopen. Process data object (PDO) for process variables and service data objects (SDO) for configuration and remote objects are re-used.

For safety applications POWERLINK can be used with the openSAFETY stack which is also available as open source.

# Technology

## Introduction

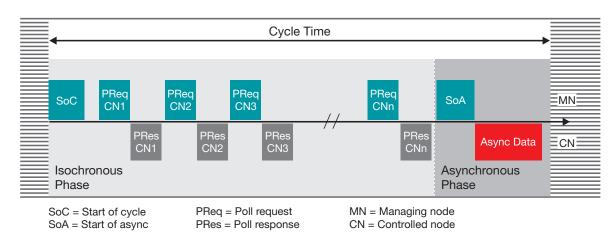

A POWERLINK system consists of a bus master (Managed Node or MN) and several slaves (Controlled Node or CN). The MN controls the bus and defines the timing and polls each CN cyclically during the isochronous phase. During that time, real-time critical data (PDO) will be transferred. The start of the isochronous phase is indicated by an

SoC message that is also used to synchronize all slaves. The isochronous phase is followed by an asynchronous phase where all non-real-time critical data such as TCP/IP traffic will happen.

*Be sure to check out the K2E Clock Generation Reference Design*

This phased approach ensures determinism on the communication bus. Ethernet POWERLINK (EPL) systems can be linked to standard Ethernet networks using gateways.

The basic idea is to have strict timing management during a POWERLINK cycle. The managing node starts the synchronous cycle, polls the nodes and finally starts the asynchronous cycle.

Start of cycle

Figure 1: POWERLINK communication scheme.

- Poll request

- Poll response by the CN

- Start of asynchronous phase

- Asynchronous data

POWERLINK operates at 100 Mbit half duplex only - the half-duplex mode enables POWERLINK to use repeaters (hubs). The Ethernet hubs used in POWERLINK networks are low-latency class Il hubs, introducing less than 460-ns delay. Half duplex comes with the advantage of using low-latency hubs but with the disadvantage of unpredictable collisions (if two nodes access the network in a close timely manner). However the POWERLINK communication scheme eliminates collisions during runtime. Contrary to a switch, a hub can forward an Ethernet frame with an extremely short delay. Combining half-duplex operation with POWERLINK's strict communication scheme provides an extreme low-latency and fully predictable network infrastructure.

In order to support POWERLINK requirements in terms of performance, determinism and low jitter it is required that the underlying media access controller (MAC) supports an auto-reply feature. Processing a poll request in a standard way by going through several levels of software on the Arm® core would introduce unpredictable delays and therefore jitter on the network. As such, the auto-reply feature is required in POWERLINK systems which allows the stack to setup pre-defined answers in registers. Any poll response can then be answered at the lowest level in the system with a minimum delay and jitter. Such a feature is ideally suited to be implemented on members of the Sitara<sup>™</sup> processor family containing a programmable real-time unit industrial communication subsystem (PRU-ICSS).

Each EPL device has a unique MAC ID (conforming to 802.3) and a node ID. Node IDs are usually assigned on the device level through switches or dials. Devices implementing a TCP/IP stack on top of POWERLINK also get an IP address consisting of a combination of a defined IP range and their node ID.

# POWERLINK solution with Sitara MPU from Texas Instruments

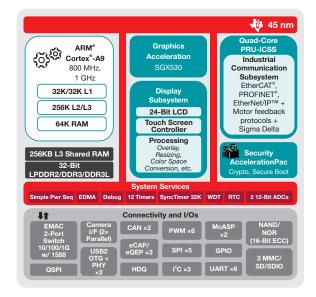

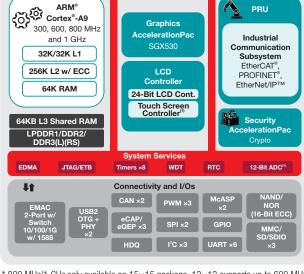

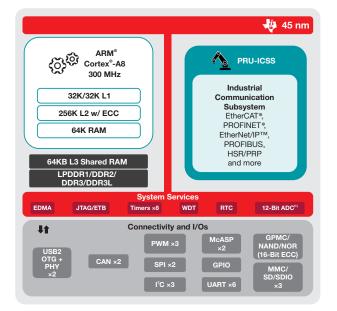

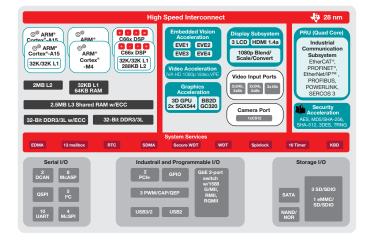

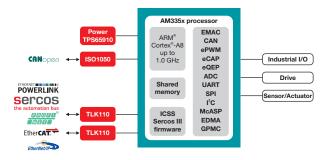

The Sitara processors - including the AMIC110, AM335x, AM437x, and AM57x - are low-power with an Arm Cortex<sup>®</sup>-A and a broad range of integrated industrial peripherals (**Figures 2-5**). The Sitara family provides scalability to help enable a wide range of applications with a performance range from 300 MHz Cortex-A8 to dual-core 1.5 GHz Cortex-A15.

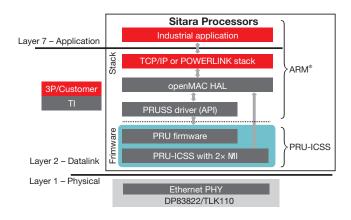

The AMIC110 and AM335x devices contain one instance of the PRU-ICSS, while the AM437x and AM57x contain two instances. The PRU-ICSS has two dedicated processing cores (Programmable Real-time Units or PRUs) and industrial communication interfaces such as universal asynchronous receiver/transmitter, media independent interface (MII) and management data input/output (MDIO). The two PRU-MII interfaces directly connect to two Ethernet PHY devices and their ports on the board. Now software can be used to implement any kind of Ethernet Media Access Control (MAC) implementation to serve different industrial protocol implementations.

For POWERLINK, TI implemented the openMAC module which is a standard Ethernet MAC with extensions for POWERLINK (e.g., auto-reply and time triggered send functions). Using openMAC on PRU-ICSS and a POWERLINK stack running on an Arm host inside the Sitara processors, it is now possible to implement an integrated POWERLINK CN or MN. The main features of the TI openMAC implementation are:

- Compliant to openMAC specification

- Two MII interfaces with 100-Mbps full-duplex and half-duplex support

🐳 45 nm

• Three-port hub implementation

- 16 Rx filters

- Ability to filter up to first 31 bytes of Rx packet

- Auto-response feature

- Time stamping of Tx and Rx packets, IRQ generation to host processor

- OS independent driver/Hardware Abstraction Layer (HAL) code

Figure 3. AM437x Sitara processor block diagram.

\* 800 MHz/1 GHz only available on 15×15 package. 13×13 supports up to 600 MHz. <sup>(1)</sup> Use of TSC will limit available ADC channels.

Figure 2: AM335x SoC block diagram.

Figure 5. AM57x block diagram.

Figure 4. AMIC110 block diagram.

**Figure 6** shows an example usage scenario for openMAC. It implements the lower layer of an Ethernet hub that is capable to be used with a POWERLINK stack. Customers can then implement POWERLINK MN on CN solutions on top.

A third-party protocol is available from Port GmbH, Halle, Germany. Port uses its own POWERLINK stack and tools that support customers in creating the required device description files and application code. The solution from port running on TI development boards was officially certified by EPSG.

Port has created a driver to interface with TI POWERLINK PRU firmware and offers features for POWERLINK products according to **Table 1**.

This solution is supported by Port's POWERLINK Design Tool (**Figure 7)** to manage complex object dictionaries.

The design tool:

- Manages object dictionary (dynamically or statically)

- Configures the POWERLINK stack accordingly

- Creates the XDD device description file

- Creates the application stubs for the customer's application

- Provides a documentation of the object dictionary

- Provides an automatic, error-free and reproducible measure to create the configuration

The design tool expands the POWERLINK offering from a simple protocol stack offering to a POWERLINK solution chain.

#### **Development tools**

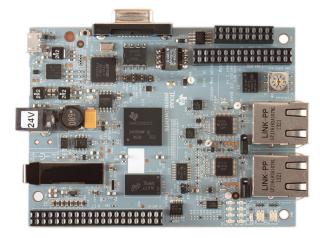

TI also provides low-cost development boards for industrial communication solution. The Industrial Communication Engines (ICEs, see **Figure 8** for an example showing the AM3359 ICE board and Industrial Development Kits) are based on a Sitara

Figure 6. openMAC usage example.

devices. They use many of the SoC peripherals such as SPI, I<sup>2</sup>C, UARTs and GPIO to drive LEDs, a display and other components such as the TLK110 or DP83822 Ethernet PHY devices on the board. For Ethernet connectivity they support two Ethernet ports that are connected to PRU-MIIs. ICE boards are equipped with SPI- and NOR-based Flash as

| Feature                           | Support |

|-----------------------------------|---------|

| Controlled node functionality     | yes     |

| Managing node functionality       | -       |

| Isochronous controlled node       | yes     |

| Async-only controlled node        | yes     |

| PD0 producer                      | yes     |

| PD0 consumer                      | yes     |

| Number of supported transmit-PDOs | 1       |

| Number of supported receive-PDOs  | 1 – 254 |

| Dynamic PDO mapping               | yes     |

| Static PDO mapping                | yes     |

| IP support                        | yes     |

| SDO-server                        | yes     |

| SDO-client                        | yes     |

| SDO over UDP                      | yes     |

| SDO over ASnd                     | yes     |

| SDO over PDO                      | -       |

| SDO expedited transfer            | yes     |

| SD0 segmented transfer            | yes     |

| Number of supported lines         | 1       |

| Multiplexing                      | yes     |

| Usage of nonvolatile memory       | yes     |

| CN NMT state machine              | yes     |

| Object dictionary                 | yes     |

| Extended data types               | yes     |

| Usage of CANopen profiles         | yes     |

| CiA-401 framework support         | yes     |

| Frame autoreply support           | yes     |

Table 1: Stack features

well as an SD card interface for permanent storage Port provides an evaluation software package that can directly be applied on the boards. The supplied

Figure 7: Port design tool.

binary application program needs to be copied onto a microSD card. Once inserted, the board can boot from an SDcard and run the POWERLINK CN implementation. Now the associated device description file may be imported into a PLC system with POWERLINK master (MN) functionality. Using the defined input and output data fields, data transfers between MN and CN can be implemented.

Figure 8: TMDSICE3359 Industrial Communication Engine (ICE) board.

The CN output data is associated in the example application with eight LEDs on the board. Data sent from the MN is directly visualized on the board.

The example application based on TI openMAC and Port POWERLINK CN stack currently supports features according to **Table 2**.

| Feature              | Description                              |

|----------------------|------------------------------------------|

| POWERLINK cycle time | 200 µs – 10000 µs                        |

| Multiplexing         | Yes                                      |

| Async MTU size       | 300–1500 bytes                           |

| Basic Ethernet mode  | Yes                                      |

| SDO                  | Using ASnd and UDP                       |

| Conformance          | POWERLINK conformance test version 1.1.0 |

| Ports                | 2 external Ethernet ports, internal hub  |

Table 2: Stack features.

Further software development can be done using the Processor Software Development Kit (Processor SDK) and protocol-specific software available on the PRU-ICSS industrial software page, which combines SYS/BIOS<sup>™</sup> [real-time operating system (RTOS) from TI] and example projects using industrial Ethernet protocols.

*Figure 9:* TMDSICE3359 Industrial Communication Engine (ICE) board system block diagram.

## Summary

The PRU-ICSS inside TI's Sitara family of processors allows implementing real-time critical Ethernet protocols in software. As such, it allows implementation of a variety of industrial communications protocols which otherwise would require an additional external FPGA or ASIC. Working with the third-party Port, TI provides a certified solution for POWERLINK CN implementations on a single System-on-Chip (SoC). Evaluation boards and related software development kits are available for customers to start their own application development. Future Sitara devices will incorporate PRU-ICSS subsystems, too, and therefore provide a scalable environment for all industrial communications needs based on a common system architecture model. Many of the available software components will be directly reusable to allow a fast and seamless transition.

## Links and resources

- EPSG: <u>www.ethernet-powerlink.org</u>

- TIDEP0028 POWERLINK CN solution: <u>www.ti.com/tool/TIDEP0028</u>

- Sitara processor family: <u>www.ti.com/sitara</u>

- PRU-ICSS industrial software: www.ti.com/tool/PRU-ICSS-INDUSTRIAL-SW

- Port solution on AM335x SoC: <u>www.port.de/en/products/applications/</u> <u>am335x.html</u>

Important Notice: The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute TI's approval, warranty or endorsement thereof.

The platform bar is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated