# Over-Current Latch Circuit with Comparator Circuit

#### **Design Goals**

| LOAD CURRENT (I <sub>L</sub> )  |             | SYSTEM SUPPLY (V <sub>S</sub> ) | COMPARATOR OUTPUT STATUS |                  |

|---------------------------------|-------------|---------------------------------|--------------------------|------------------|

| Over Current (I <sub>OC</sub> ) | Recovery    | Typical                         | Over Current             | Normal Operation |

| 10 A                            | Power Cycle | 24 V                            | > V <sub>S</sub> - 0.4 V | < 0.4 V          |

#### **Design Description**

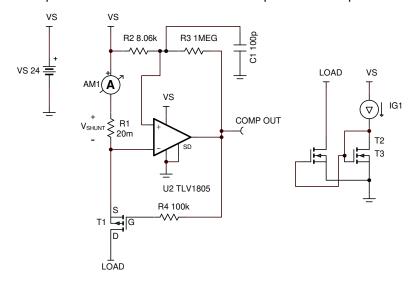

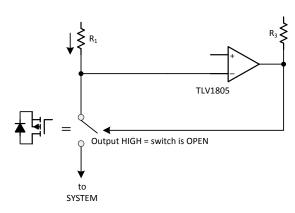

This high-side, current sensing solution uses a high-voltage, rail-to-rail input comparator and a p-channel MOSFET to create an over-current (OC) latch circuit. The OC output signal from the comparator is a logic-high level when the load current exceeds 10 A. The logic-high output level turns the MOSFET switch off and disconnects the load from the system supply ( $V_S$ ). The comparator output also drives the bottom of the R2/R3 resistor divider which controls the OC threshold level. Under normal operating current levels, the bottom of the resistor divider is held low at ground potential. However, when the OC level is exceeded, the comparator output goes high and elevates the non-inverting input of the comparator to a level equal to  $V_S$ . Due to the integrated hysteresis of the comparator, the comparator output will remain high and thus a latched output condition is achieved. Only power-cycling  $V_S$  will remove the latched output condition. The shutdown pin could also be utilized to clear the latch if a pull-down resistor is added at the output of the comparator.

#### **Design Notes**

- 1. Select a comparator with rail-to-rail input common mode range to enable high-side current sensing.

- 2. Select a comparator with a push-pull output stage to efficiently drive the p-channel MOSFET.

- 3. Select a comparator with low input offset voltage to optimize accuracy.

- 4. Select a comparator with integrated hysteresis to create a latched-output condition.

#### **Design Steps**

Select the value of shunt resistor (R1) so the shunt voltage (V<sub>SHUNT</sub>) is at least 10x greater than the comparator input offset voltage (V<sub>IO</sub>). Note that making R1 very large will improve OC detection accuracy but will reduce supply headroom.

$$\begin{split} &V_{SHUNT}=(I_{OC}\times R_1)\geq 10\times V_{IO}\\ &\text{for }I_{OC}=10A \ \& \ V_{IO}=6.5\text{mV} \ \text{(max value for TLV1805), VSHUNT}\geq 65\text{mV}\\ &\text{set }R_1=20\text{m}\Omega \ \text{ so that } V_{SHUNT}=200\text{mV} \ \text{for }I_{OC}=10A \end{split}$$

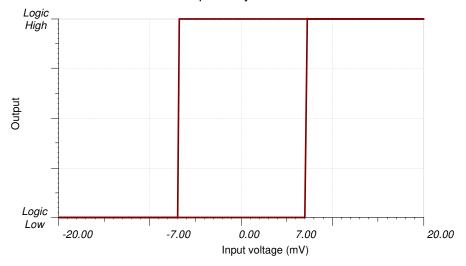

2. Since a comparator with integrated hysteresis is being utilized, the hysteresis needs to be accommodated for in the design. Note how a comparator with integrated hysteresis does not transition from high-to-low and from low-to-high at the same input voltage level. In the case of the TLV1805, the hysteresis is 14 mV and thus the transition thresholds are at ±7 mV respectively.

#### **TLV1805 Transition Thresholds**

3. A good way to model a comparator internal hysteresis is shown below. One can think of hysteresis as offset that is intentionally added to the design. When the output of the comparator is low, a voltage source equivalent to V<sub>HYS</sub>/2 is added in series with the inverting input pin. However, when the comparator output is high, the hysteresis is modeled as a voltage source of the same value added in series with the non-inverting input.

$$V_{HVS}/2 = 7mV$$

TLV1805

OUT = Low

# **Comparator Output Low**

$$V_{HYS}/2 = 7mV$$

TLV1805

OUT = High

#### **Comparator Output High**

4. Select the values of resistor divider R2 and R3 so the comparator output will transition from low-to-high when V<sub>SHUNT</sub> exceeds 200 mV. Since the output of the comparator will be *low* prior to an OC condition occuring, use the Comparator Output Low model. The integrated hysteresis effectively shifts the switching threshold from V<sub>S</sub> - 200 mV to V<sub>S</sub> - 193 mV in the case of the TLV1805 which has an integrated hysteresis value of 14mV. Recall that 1/2 of the hysteresis is applied since hysteresis is defined as the difference between the two switching thresholds of a comparator.

5. The following equation is used to solve for R2 and R3.

$$\begin{split} R_2 &= \frac{(V_{SHUNT} - V_{HYS}/2) \times R3}{V_S - (V_{SHUNT} - V_{HYS}/2)} \\ \text{for } V_S &= 24V, \quad V_{SHUNT} = 200 \text{mV}, \quad V_{HYS} = 14 \text{mV} \quad \text{and} \quad R3 = 1 \text{M}\Omega \\ R2 &= \frac{(200 \text{m} - 14 \text{m}/2) \times 1 \text{M}}{24 - (200 \text{m} - 14 \text{m}/2)} \end{split}$$

$$R2 = 8.107k\Omega$$

(closest 1% value is  $8.06k\Omega$ )

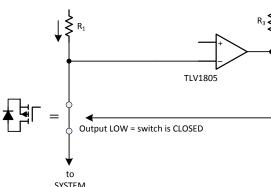

6. Since the goal of this design is to create a circuit that will disconnect the load from the system supply when an OC condition occurs, the output of the comparator is connected to the gate of a p-channel MOSFET switch. Recall that a p-ch MOSFET will look like a closed switch when the source to gate voltage is greater than the voltage threshold (V<sub>SG</sub> > V<sub>TH</sub>). Likewise, the MOSFET will look like an open-circuit when V<sub>SG</sub> < V<sub>TH</sub> (see figures below).

## Normal Operation = Output LOW and CLOSED Switch

#### OC Condition = Output HIGH and OPEN Switch

- 7. Add a series resistor (R4) between the comparator output and the gate of the MOSFET to limit the output current during the transition from low to high. Keeping the current in the mA range is sufficient. Selecting a value of 10 k $\Omega$  for R1, the current is limited to 2.4 mA (24 V/10 k $\Omega$ ).

- 8. The other goal of this design is to latch the circuit when an OC condition occurs. This is accomplished by providing feedback to the resistor divider network of R2/R3. When the output of the comparator goes high, it turns off the MOSFET and raises the non-inverting node of the comparator to a voltage level of V<sub>S</sub>.

- 9. Note that V<sub>SHUNT</sub> also reduces to 0 V since the load current is now 0 A. The hysteresis of the comparator that was previously mentioned in Design Step 2 will keep the non-inverting input 7 mV higher than the inverting input. This is what latches the comparator output in a logic high state.

- 10. Lastly, capacitor C1 is connected from the non-inverting input to ground to make sure that the comparator starts in the logic low output state as V<sub>S</sub> rises upon initial power-up.

## **Design Simulations**

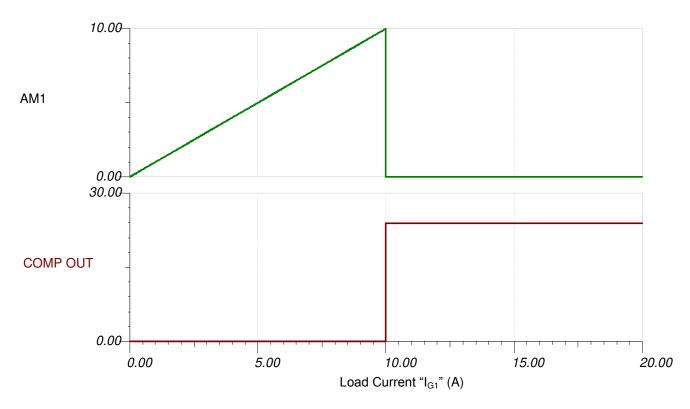

## **DC Simulation Results**

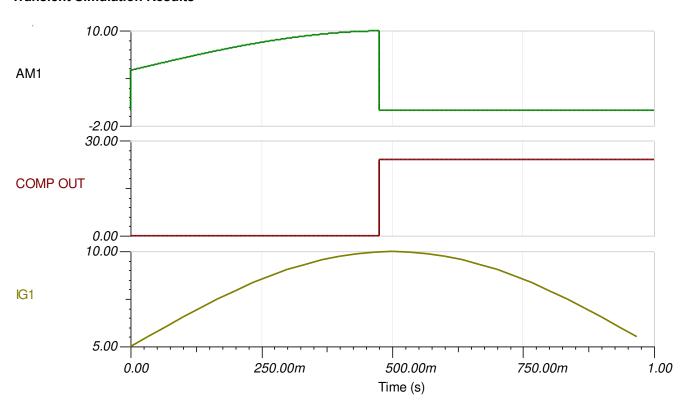

## **Transient Simulation Results**

## **Design References**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

See Circuit SPICE Simulation File, SLOM456.

## **Design Featured Comparator**

| TLV1805-Q1, TLV1805 |               |  |  |

|---------------------|---------------|--|--|

| $v_s$               | 3.3 V to 40 V |  |  |

| V <sub>inCM</sub>   | Rail-to-rail  |  |  |

| V <sub>OUT</sub>    | Push-Pull     |  |  |

| Vos                 | 500 μV        |  |  |

| IQ                  | 135 μΑ        |  |  |

| t <sub>PD(HL)</sub> | 250 ns        |  |  |

| #Channels           | 1             |  |  |

| TLV1805-Q1, TLV1805 |               |  |  |

## **Design Alternate Comparator**

|                     | LMC6762       | TLV370x-Q1, TLV370x |  |

|---------------------|---------------|---------------------|--|

| Vs                  | 2.7 V to 15 V | 2.7 V to 16 V       |  |

| V <sub>inCM</sub>   | Rail-to-rail  | Rail-to-rail        |  |

| V <sub>OUT</sub>    | Push-Pull     | Push-Pull           |  |

| Vos                 | 3 mV          | 250 μV              |  |

| IQ                  | 20 μΑ         | 560 nA/Ch           |  |

| t <sub>PD(HL)</sub> | 4 µs          | 36 µs               |  |

| #Channels           | 1             | 1, 2, and 4         |  |

|                     | LMC6762       | TLV370x-Q1, TLV370x |  |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated