# Errata

# TMS320F2837xS Real-Time MCUs Silicon Errata Silicon Revisions C, B

#### **ABSTRACT**

This document describes the known exceptions to the functional specifications (advisories). This document may also contain usage notes. Usage notes describe situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness.

# **Table of Contents**

| 1 Usage Notes and Advisories Matrices                                                              |    |

|----------------------------------------------------------------------------------------------------|----|

| 1.1 Usage Notes Matrix                                                                             | 2  |

| 1.2 Advisories Matrix                                                                              | 2  |

| 2 Nomenclature, Package Symbolization, and Revision Identification                                 | 4  |

| 2.1 Device and Development Support Tool Nomenclature                                               | 4  |

| 2.2 Devices Supported                                                                              |    |

| 2.3 Package Symbolization and Revision Identification                                              | 5  |

| 3 Silicon Revision C Usage Notes and Advisories                                                    | 7  |

| 3.1 Silicon Revision C Usage Notes                                                                 |    |

| 3.2 Silicon Revision C Advisories                                                                  |    |

| 4 Silicon Revision B Usage Notes and Advisories                                                    | 41 |

| 4.1 Silicon Revision B Usage Notes                                                                 | 41 |

| 4.2 Silicon Revision B Advisories                                                                  | 41 |

| 5 Documentation Support                                                                            | 46 |

| 6 Trademarks                                                                                       | 46 |

| 7 Revision History                                                                                 | 47 |

|                                                                                                    |    |

| List of Figures                                                                                    |    |

| Figure 2-1. Example of Package Symbolization – ZWT                                                 | 5  |

| Figure 2-2. Example of Package Symbolization – PTP                                                 |    |

| Figure 2-3. Example of Device Nomenclature                                                         |    |

| Figure 3-1. Pipeline Diagram of the Issue When There are no Stalls in the Pipeline                 |    |

| Figure 3-2. Pipeline Diagram of the Issue if There is a Stall in the E3 Slot of the Instruction I1 |    |

| Figure 3-3. Pipeline Diagram With Workaround in Place                                              |    |

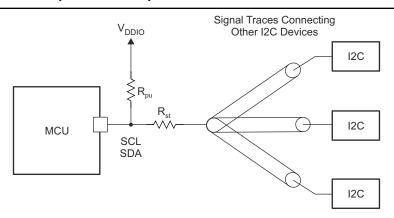

| Figure 3-4. Placement of Series Termination Resistor and Pullup Resistor                           |    |

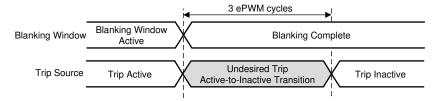

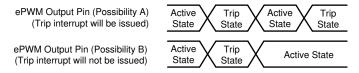

| Figure 3-5. Undesired Trip Event and Blanking Window Expiration                                    |    |

| Figure 3-6. Resulting Undesired ePWM Outputs Possible                                              |    |

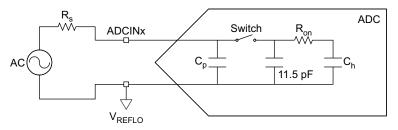

| Figure 4-1. Single-Ended Input Model                                                               |    |

|                                                                                                    |    |

| List of Tables                                                                                     |    |

| Table 1-1. Usage Notes Matrix                                                                      | 2  |

| Table 1-2. Advisories Matrix                                                                       |    |

| Table 2-1. Determining Silicon Revision From Lot Trace Code                                        |    |

| Table 3-1. Bandgap Usage by Module                                                                 |    |

| Table 3-2. Memories Impacted by Advisory                                                           |    |

| Table 3-3. Data Rise Time Requirements for C2000 as Target Transmitter with Standard-Mode Host     |    |

| Table 3-4. Pullup Resistor (R <sub>p</sub> ) Values for Common Bus Capacitances (C <sub>b</sub> )  |    |

| · · · · · · · · · · · · · · · · · · ·                                                              |    |

# 1 Usage Notes and Advisories Matrices

Table 1-1 lists all usage notes and the applicable silicon revisions. Table 1-2 lists all advisories, modules affected, and the applicable silicon revisions.

# 1.1 Usage Notes Matrix

**Table 1-1. Usage Notes Matrix**

| NUMBER        | TITLE                                                                                                                                                    | SILICON REVISIONS<br>AFFECTED |     |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----|--|--|--|

|               |                                                                                                                                                          | В                             | С   |  |  |  |

| Section 3.1.1 | PIE: Spurious Nested Interrupt After Back-to-Back PIEACK Write and Manual CPU Interrupt Mask Clear                                                       | Yes                           | Yes |  |  |  |

| Section 3.1.2 | Caution While Using Nested Interrupts                                                                                                                    | Yes                           | Yes |  |  |  |

| Section 3.1.3 | SYS/BIOS: Version Implemented in Device ROM is not Maintained                                                                                            | Yes                           | Yes |  |  |  |

| Section 3.1.4 | SDFM: Use Caution While Using SDFM Under Noisy Conditions                                                                                                | Yes                           | Yes |  |  |  |

| Section 3.1.5 | McBSP: XRDY Bit can Hold the Not-Ready Status (0) if New Data is Written to the DX1 Register Without Verifying if the XRDY Bit is in its Ready State (1) | Yes                           | Yes |  |  |  |

# 1.2 Advisories Matrix

**Table 1-2. Advisories Matrix**

| MODULE | DESCRIPTION                                                                                                                    |     | REVISIONS<br>CTED |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------|-----|-------------------|--|

|        |                                                                                                                                | В   | С                 |  |

|        | Analog Bandgap References                                                                                                      | Yes | Yes               |  |

|        | Analog Trim of Some TMX Devices                                                                                                | Yes |                   |  |

| ADC    | ADC: ADC Post-Processing Block Limit Compare                                                                                   | Yes | Yes               |  |

| ADC    | ADC: Interrupts may Stop if INTxCONT (Continue-to-Interrupt Mode) is not Set                                                   | Yes | Yes               |  |

| ADC    | ADC: ADC Offset Trim in Different Modes                                                                                        | Yes | Yes               |  |

| ADC    | ADC: DMA Read of Stale Result                                                                                                  | Yes | Yes               |  |

| ADC    | ADC: Random Conversion Errors                                                                                                  | Yes |                   |  |

| ADC    | ADC: ADC PPB Event Trigger (ADCxEVT) to ePWM Digital Compare Submodule                                                         | Yes |                   |  |

| ADC    | ADC: 12-Bit Switch Resistance                                                                                                  | Yes |                   |  |

| ADC    | ADC: 12-Bit Input Capacitance When Switching Channel Groups                                                                    | Yes |                   |  |

|        | XRS may Toggle During Power Up                                                                                                 | Yes |                   |  |

| CLB    | CLB: Back-to-Back PUSH or PULL Instructions With More Than One Active High-<br>Level Controller (HLC) Channel is Not Supported | Yes | Yes               |  |

| USB    | USB: USB DMA Event Triggers are not Supported                                                                                  | Yes | Yes               |  |

| VREG   | VREG: VREG Will be Enabled During Power Up Irrespective of VREGENZ                                                             | Yes |                   |  |

| Flash  | Flash: A Single-Bit ECC Error May Cause Endless Calls to Single-Bit-Error ISR                                                  | Yes | Yes               |  |

| Flash  | Flash: Minimum Programming Word Size                                                                                           | Yes | Yes               |  |

| ePIE   | ePIE: Spurious VCU Interrupt (ePIE 12.6) Can Occur When First Enabled                                                          | Yes |                   |  |

| eQEP   | eQEP: Position Counter Incorrectly Reset on Direction Change During Index                                                      | Yes | Yes               |  |

| eQEP   | eQEP: eQEP Inputs in GPIO Asynchronous Mode                                                                                    | Yes | Yes               |  |

| HWBIST | HWBIST: Avoiding Spurious Interrupts While Using HWBIST                                                                        | Yes | Yes               |  |

| PLL    | PLL: May Not Lock on the First Lock Attempt                                                                                    | Yes | Yes               |  |

| PLL    | PLL: Power Down and Bypass May Take up to 120 SYSCLK Cycles to be Effective                                                    | Yes | Yes               |  |

| SDFM   | SDFM: Data Filter Output Does Not Saturate at Maximum Value With Sinc3 and OSR = 256                                           | Yes | Yes               |  |

| SDFM   | SDFM: Spurious Data Acknowledge Event When Data Filter is Configured and Enabled for the First Time                            | Yes | Yes               |  |

| SDFM   | SDFM: Spurious Data Acknowledge Event When Data Filter is Synchronized Using PWM FILRES Signal                                 | Yes | Yes               |  |

Table 1-2. Advisories Matrix (continued)

| MODULE                                                       | DESCRIPTION                                                                                                                     | SILICON REVISIONS<br>AFFECTED |     |  |  |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----|--|--|

| ODEM Comments Filter Madels are a Comment Commission Co. 144 |                                                                                                                                 | В                             | С   |  |  |

| SDFM                                                         | SDFM: Comparator Filter Module may Generate Spurious Over-Value and Under-Value Conditions                                      | Yes                           | Yes |  |  |

| SDFM                                                         | SDFM: Dynamically Changing Threshold Settings (LLT, HLT), Filter Type, or COSR Settings Will Trigger Spurious Comparator Events | Yes                           | Yes |  |  |

| SDFM                                                         | SDFM: Dynamically Changing Data Filter Settings (Such as Filter Type or DOSR) Will Trigger Spurious Data Acknowledge Events     | Yes                           | Yes |  |  |

| SDFM                                                         | SDFM: Manchester Mode (Mode 2) Does Not Produce Correct Filter Results Under Several Conditions                                 | Yes                           | Yes |  |  |

| FPU                                                          | FPU: FPU-to-CPU Register Move Operation Preceded by Any FPU 2p Operation                                                        | Yes                           | Yes |  |  |

| FPU                                                          | FPU: LUF, LVF Flags are Invalid for the EINVF32 and EISQRTF32 Instructions                                                      | Yes                           | Yes |  |  |

| Memory                                                       | Memory: Prefetching Beyond Valid Memory                                                                                         | Yes                           | Yes |  |  |

| INTOSC                                                       | INTOSC: V <sub>DDOSC</sub> Powered Without V <sub>DD</sub> Can Cause INTOSC Frequency Drift                                     | Yes                           | Yes |  |  |

| Low-Power Modes                                              | Low-Power Modes: Power Down Flash or Maintain Minimum Device Activity                                                           | Yes                           | Yes |  |  |

| I2C                                                          | I2C: SDA and SCL Open-Drain Output Buffer Issue                                                                                 | Yes                           | Yes |  |  |

| I2C                                                          | I2C: Target Transmitter Mode, Standard Mode SDA Timings Limitation                                                              | Yes                           | Yes |  |  |

| ePWM                                                         | ePWM: An ePWM Glitch can Occur if a Trip Remains Active at the End of the Blanking Window                                       | Yes                           | Yes |  |  |

| ePWM                                                         | ePWM: ePWM Dead-Band Delay Value Cannot be Set to 0 When Using Shadow Load Mode for RED/FED                                     | Yes                           | Yes |  |  |

| ePWM                                                         | ePWM: Trip Events Will Not be Filtered by the Blanking Window for the First 3 Cycles After the Start of a Blanking Window       | Yes                           | Yes |  |  |

| SYSTEM                                                       | SYSTEM: Multiple Successive Writes to CLKSRCCTL1 Can Cause a System Hang                                                        | Yes                           | Yes |  |  |

| CMPSS                                                        | CMPSS: COMPxLATCH May Not Clear Properly Under Certain Conditions                                                               | Yes                           | Yes |  |  |

| CMPSS                                                        | CMPSS: Ramp Generator May Not Start Under Certain Conditions                                                                    | Yes                           | Yes |  |  |

| GPIO                                                         | GPIO: Open-Drain Configuration May Drive a Short High Pulse                                                                     | Yes                           | Yes |  |  |

|                                                              | During DCAN FIFO Mode, Received Messages May be Placed Out of Order in the FIFO Buffer                                          | Yes                           | Yes |  |  |

| Boot ROM                                                     | Boot ROM: Calling SCI Bootloader from Application                                                                               | Yes                           | Yes |  |  |

| Boot ROM                                                     | Boot ROM: Device Will Hang During Boot if X1 Clock Source is not Present                                                        | Yes                           |     |  |  |

|                                                              |                                                                                                                                 |                               |     |  |  |

# 2 Nomenclature, Package Symbolization, and Revision Identification

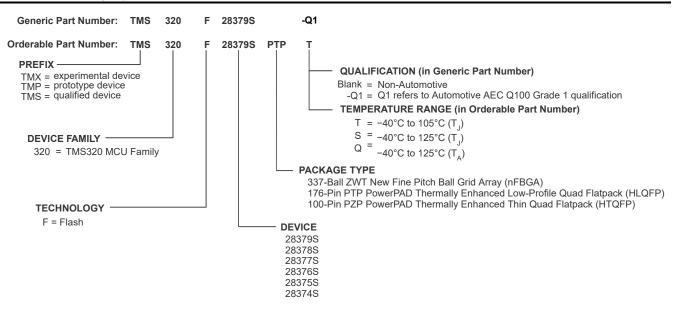

# 2.1 Device and Development Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all [TMS320] DSP devices and support tools. Each TMS320™ DSP commercial family member has one of three prefixes: TMX, TMP, or TMS (for example, **TMS** 320F28379S). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (with TMX for devices and TMDX for tools) through fully qualified production devices and tools (with TMS for devices and TMDS for tools).

Device development evolutionary flow:

- **TMX** Experimental device that is not necessarily representative of the final device's electrical specifications and may not use production assembly flow.

- **TMP** Prototype device that is not necessarily the final silicon die and may not necessarily meet final electrical specifications.

**TMS** Production version of the silicon die that is fully qualified.

Support tool development evolutionary flow:

**TMDX** Development-support product that has not yet completed Texas Instruments internal qualification testing.

**TMDS** Fully-qualified development-support product.

TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

Production devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. Tl's standard warranty applies.

Predictions show that prototype devices (X or P) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

TI device nomenclature also includes a suffix with the device family name. This suffix indicates the package type (for example, PTP) and temperature range (for example, T).

# 2.2 Devices Supported

This document supports the following devices:

- TMS320F28379S

- TMS320F28378S

- TMS320F28377S

- TMS320F28377S-Q1

- TMS320F28376S

- TMS320F28375S

- TMS320F28375S-Q1

- TMS320F28374S

# 2.3 Package Symbolization and Revision Identification

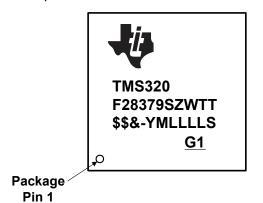

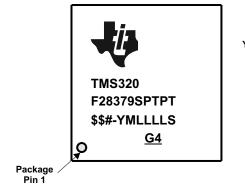

Figure 2-1 and Figure 2-2 provide examples of the 2837xS device markings and define each of the markings. The device revision can be determined by the symbols marked on the top of the package as shown in Figure 2-1 and Figure 2-2. Some prototype devices may have markings different from those illustrated. Figure 2-3 shows an example of the device nomenclature.

YMLLLLS = Lot Trace Code

YM = 2-digit Year/Month Code

LLLL = Assembly Lot Code

S = Assembly Site Code

\$\$ = Wafer Fab Code (one or two characters as applicable)

& = PG Revision

G1 = Green (Low Halogen and RoHS-compliant)

Figure 2-1. Example of Package Symbolization - ZWT

YMLLLLS = Lot Trace Code

YM = 2-Digit Year/Month Code LLLL = Assembly Lot

S = Assembly Site Code

\$\$ = Wafer Fab Code as applicable # = Silicon Revision Code

G4 = Green (Low Halogen and RoHS-compliant)

Figure 2-2. Example of Package Symbolization – PTP

Table 2-1. Determining Silicon Revision From Lot Trace Code

| SILICON REVISION CODE | SILICON REVISION | REVID <sup>(1)</sup> Address: 0x5D00C | COMMENTS                                   |

|-----------------------|------------------|---------------------------------------|--------------------------------------------|

| В                     | ВВВ              |                                       | This silicon revision is available as TMX. |

| C C                   |                  | 0x0003                                | This silicon revision is available as TMS. |

(1) Silicon Revision ID

Figure 2-3. Example of Device Nomenclature

# 3 Silicon Revision C Usage Notes and Advisories

This section lists the usage notes and advisories for this silicon revision.

# 3.1 Silicon Revision C Usage Notes

This section lists all the usage notes that are applicable to silicon revision C [and earlier silicon revisions].

# 3.1.1 PIE: Spurious Nested Interrupt After Back-to-Back PIEACK Write and Manual CPU Interrupt Mask Clear

Revisions Affected: B, C

Certain code sequences used for nested interrupts allow the CPU and PIE to enter an inconsistent state that can trigger an unwanted interrupt. The conditions required to enter this state are:

- 1. A PIEACK clear is followed immediately by a global interrupt enable (EINT or asm(" CLRC INTM")).

- 2. A nested interrupt clears one or more PIEIER bits for its group.

Whether the unwanted interrupt is triggered depends on the configuration and timing of the other interrupts in the system. This is expected to be a rare or nonexistent event in most applications. If it happens, the unwanted interrupt will be the first one in the nested interrupt's PIE group, and will be triggered after the nested interrupt reenables CPU interrupts (EINT or asm(" CLRC INTM")).

**Workarounds:** Add a NOP between the PIEACK write and the CPU interrupt enable. Example code is shown below.

# 3.1.2 Caution While Using Nested Interrupts

#### Revisions Affected: B, C

If the user is enabling interrupts using the EINT instruction inside an interrupt service routine (ISR) in order to use the nesting feature, then the user must disable the interrupts before exiting the ISR. Failing to do so may cause undefined behavior of CPU execution.

# 3.1.3 SYS/BIOS: Version Implemented in Device ROM is not Maintained

# Revisions Affected: B, C

The SYS/BIOS version 6.37 in ROM cannot be updated to address bug fixes or enhancements. For applications using this ROM version of SYS/BIOS, the user should review the release notes on the SYS/BIOS Product Releases page to assess any application impact to known bugs.

To use the latest maintained SYS/BIOS version, download the SYS/BIOS library and include in the application flash image instead of using the ROM version.

# 3.1.4 SDFM: Use Caution While Using SDFM Under Noisy Conditions

Revisions Affected: B, C

The SDFM clock input (SDx\_Cy) directly clocks the SDFM module when there is no GPIO input synchronization. Any glitches or ringing noise on the SDx\_Cy input beyond  $V_{IH}$  or  $V_{IL}$  can corrupt the SDFM module, leading to unpredictable results.

#### Workarounds:

# **SDFM GPIO Asynchronous Mode:**

Special attention should be taken during board design to ensure a clean and noise-free signal that meets the SDFM timing requirements. Precautions such as series termination for ringing due to any impedance mismatch of the clock driver, and spacing of traces from other high-frequency signals are recommended.

# SDFM GPIO Qualification (3-sample) Mode:

It is highly recommended that the SDFM GPIO qualification mode be used in noisy conditions. This mode provides additional protection by filtering both SDx\_Cy and SDx\_Dy inputs from system noise. Refer to the "SDFM Timing Requirements When Using GPIO Input Qualification (3-Sample Window)" table in the TMS320F2837xS Real-Time Microcontrollers data sheet when using this option.

When a noise event occurs while using the GPIO Qualification mode, there may still be data disturbance, but it will be proportional to the duration of the noise event and typically filtered by the oversampling of the SDFM module. Below is a relative listing of each SDFM mode's sensitivity to data variation in the presence of severe system noise.

- Mode 0: This mode is the best performing mode. It is the recommended mode under noisy conditions.

- Mode 1 and Mode 3: The error in these modes can be twice as large as the error in Mode 0 since each noise glitch can introduce error for multiple data bits.

- Mode 2: This option is unavailable when using GPIO qualification. This mode is not recommended for either GPIO ASYNC or GPIO qualification.

# 3.1.5 McBSP: XRDY Bit can Hold the Not-Ready Status (0) if New Data is Written to the DX1 Register Without Verifying if the XRDY Bit is in its Ready State (1)

Revisions Affected: B, C

If the XRDY bit is used to properly gate writes to the DX2/DX1 registers, this condition will not occur.

Per the operation of the McBSP, a write to the DX1 data transmit register will automatically clear the XRDY bit, indicating a not-ready status. Once this data is transferred to the internal transmit shift register (XSR1), the McBSP HW will set the XRDY bit, indicating a ready status, and new data can be written to DX2/DX1 data transmit registers.

If the set and clear of XRDY occur on the same CPU clock cycle, the XRDY bit will remain cleared and the new data in the DX2/DX1 will not be transmitted.

In this state of XRDY = 0, the McBSP will be in the not-ready status indefinitely.

Any subsequent writes to DX2/DX1 will behave normally and the XRDY bit will function as normal.

# Workarounds:

When transmitting multiple words of data using the McBSP module, poll the XRDY bit in the SPCR2 register before writing new data to the DX2/DX1 registers to prevent overwriting. For those modules that do not have access to the XRDY bit (such as the DMA controller), the XINT interrupt inside the McBSP module can be configured to reflect XRDY (through the XINTM bits in SPCR2 register), and this can also be used to gate writes to the DX2/DX1 registers. This will also ensure that the XRDY bit is not set and cleared on the same CPU cycle, causing the above "not-ready indefinitely" condition.

If the system allows multiple bus controllers, such as the C28x CPU and the DMA controller, to write to the DX2/DX1 registers, then the ready state of the XRDY bit should be validated before passing control of the McBSP to a different bus controller. This will ensure that the state of XRDY is accurate and the simultaneous set/clear action does not occur.

#### 3.2 Silicon Revision C Advisories

This section lists all the advisories that are applicable to silicon revision C [and earlier silicon revisions].

Advisory

Analog Bandgap References

**Revisions Affected**

B, C

**Details**

The Analog Subsystem includes internal bandgap reference circuits that are shared by the embedded analog modules. Table 3-1 shows the bandgap usage by module.

Table 3-1. Bandgap Usage by Module

| BANDGAP | ADC  | BUFFERED DAC | CMPSS            |

|---------|------|--------------|------------------|

| BGA     | ADCA | DACA<br>DACB | CMPSS1<br>CMPSS2 |

| BGB     | ADCB | DACC         | CMPSS3<br>CMPSS4 |

| BGC     | ADCC |              | CMPSS5<br>CMPSS6 |

| BGD     | ADCD |              | CMPSS7<br>CMPSS8 |

Each bandgap reference—BGA, BGB, BGC, or BGD—will power up when one or more of the dependent modules are enabled. An active bandgap reference will power down if all dependent modules are disabled.

For example, bandgap B (BGB) is powered down unless one or more of the following register bits are set:

- AdcbRegs.ADCCTL1.bit.ADCPWDNZ

- DaccRegs.DACOUTEN.bit.DACOUTEN

- Cmpss3Regs.COMPCTL.bit.COMPDACE

- Cmpss4Regs.COMPCTL.bit.COMPDACE

The CMPSS and GPDAC power-up time specification in the *TMS320F2837xS Real-Time Microcontrollers* data sheet previously did not account for the bandgap power-up time. This 10-µs value has been increased to 500 µs to account for the bandgap power-up time.

# Workarounds

If your application was utilizing a power-up time of 10  $\mu$ s for the CMPSS and GPDAC, you do not need to increase it to 500  $\mu$ s if the respective ADC on that bandgap was turned on before the CMPSS and GPDAC, and the ADC power-up time of 500  $\mu$ s was adhered to.

For simplicity, it is recommended that 500  $\mu s$  be used as the power-up time for both CMPSS and GPDAC.

# ADC: ADC Post-Processing Block Limit Compare

#### **Revisions Affected**

B, C

#### **Details**

When using a non-zero offset reference in the ADC post-processing block (PPB), the resultant ADCPPBxRESULT can be signed. TRIPHI or TRIPLO limit compares do not function correctly with this result if it is signed.

#### Workarounds

When using the TRIPHI or TRIPLO limit compares, leave the offset reference as zero. The offset reference (and zero compare) can be used as long as the limit compares are disabled.

If the limit compares, the offset reference, and the zero-crossing compare are to be used at the same time, then two PPBs can be used. Both PPBs should be configured to use the same SOC. One PPB can implement the TRIPHI and/or TRIPLO limit compares while the other can implement offset reference subtraction and zero-crossing detection.

# Advisory

# ADC: Interrupts may Stop if INTxCONT (Continue-to-Interrupt Mode) is not Set

#### **Revisions Affected**

B, C

#### **Details**

If ADCINTSELxNx[INTxCONT] = 0, then interrupts will stop when the ADCINTFLG is set and no additional ADC interrupts will occur.

When an ADC interrupt occurs simultaneously with a software write of the ADCINTFLGCLR register, the ADCINTFLG will unexpectedly remain set, blocking future ADC interrupts.

#### Workarounds

Use Continue-to-Interrupt Mode to prevent the ADCINTFLG from blocking additional ADC interrupts:

```

ADCINTSEL1N2[INT1CONT] = 1;

ADCINTSEL1N2[INT2CONT] = 1;

ADCINTSEL3N4[INT3CONT] = 1;

ADCINTSEL3N4[INT4CONT] = 1;

```

- 2. Ensure there is always sufficient time to service the ADC ISR and clear the ADCINTFLG before the next ADC interrupt occurs to avoid this condition.

- Check for an overflow condition in the ISR when clearing the ADCINTFLG.

Check ADCINTOVF immediately after writing to ADCINTFLGCLR; if it is set, then write ADCINTFLGCLR a second time to ensure the ADCINTFLG is cleared. The ADCINTOVF register will be set, indicating an ADC conversion interrupt was lost.

```

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1;  //clear INT1 flag if(1 == AdcaRegs.ADCINTOVF.bit.ADCINT1)  //ADCINT overflow {

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1;  //clear INT1 again // If the ADCINTOVF condition will be ignored by the application // then clear the flag here by writing 1 to ADCINTOVFCLR. // If there is a ADCINTOVF handling routine, then either insert // that code and clear the ADCINTOVF flag here or do not clear // the ADCINTOVF here so the external routine will detect the // condition. // AdcaRegs.ADCINTOVFCLR.bit.ADCINT1 = 1;  // clear OVF }

```

#### ADC: ADC Offset Trim in Different Modes

#### **Revisions Affected**

B, C

#### **Details**

A different offset trim is required when switching between 12-bit and 16-bit resolution and when switching between single-ended and differential signaling mode.

#### Workarounds

Whenever setting the resolution or signal mode of the ADC, use the "AdcSetMode" function in C2000Ware. This will ensure the correct trims are loaded into the offset trim register. Note that on start-up, offset and linearity trims are not loaded, and must be populated by calling AdcSetMode() from the user application.

#### **Advisory**

#### ADC: DMA Read of Stale Result

#### **Revisions Affected**

B, C

#### **Details**

The ADCINT flag can be set before the ADCRESULT value is latched (see the  $t_{LAT}$  and  $t_{INT(LATE)}$  columns in the ADC Timings tables of the TMS320F2837xS Real-Time Microcontrollers data sheet). The DMA can read the ADCRESULT value as soon as 3 cycles after the ADCINT trigger is set. As a result, the DMA could read a prior ADCRESULT value when the user expects the latest result if all of the following are true:

- The ADC is in late interrupt mode.

- The ADC operates in a mode where t<sub>INT(LATE)</sub> occurs 3 or more cycles before t<sub>LAT</sub> (ADCCTL2 [PRESCALE] > 2 for 12-bit mode).

- The DMA is triggered from the ADCINT signal.

- The DMA immediately reads the ADCRESULT value associated with that ADCINT signal without reading any other values first.

- The DMA was idle when it received the ADCINT trigger.

Only the DMA reads listed above could result in reads of stale data; the following non-DMA methods will always read the expected data:

- The ADCINT flag triggers a CLA task.

- The ADCINT flag triggers a CPU ISR.

- · The CPU polls the ADCINT flag.

#### Workarounds

Trigger two DMA channels from the ADCINT flag. The first channel acts as a dummy transaction. This will result in enough delay that the second channel will always read the fresh ADC result.

Advisory CLB: Back-to-Back PUSH or PULL Instructions With More Than One Active High-

Level Controller (HLC) Channel is Not Supported

**Revisions Affected**

B, C

**Details**

This issue only affects HLC operations if using back-to-back PUSH or PULL instructions

with more than one active HLC channel.

Workarounds

Re-order the HLC instructions so that every PUSH instruction is followed by a non-PUSH instruction. The same applies for the PULL instruction. If only one HLC channel is active,

this issue does not occur.

Advisory

USB: USB DMA Event Triggers are not Supported

**Revisions Affected**

B, C

**Details**

The USB module generates inadvertent extra DMA requests, causing the FIFO to

overflow (on IN endpoints) or underflow (on OUT endpoints). This causes invalid IN DATA

packets (larger than the maximum packet size) and duplicate receive data.

Workarounds

None

# Flash: A Single-Bit ECC Error May Cause Endless Calls to Single-Bit-Error ISR

#### **Revisions Affected**

B, C

#### **Details**

When a single-bit ECC error is detected, the CPU executes the single-bit-error interrupt service routine (ISR). When the ISR returns, the same instruction that caused the first error is fetched again. If the ECC error threshold (ERR\_THRESHOLD.THRESHOLD) is 0, then the same error is detected and another ISR is executed. This continues in an endless loop. This sequence of events only occurs if the error is caused by a program fetch operation, not a data read.

#### Workarounds

Set the error threshold bit-field (ERR\_THRESHOLD.THRESHOLD) to a value greater than or equal to 1. Note that the default value of the threshold bit-field is 0.

# **Advisory**

# Flash: Minimum Programming Word Size

#### **Revisions Affected**

B, C

#### **Details**

The Main Array flash programming must be aligned to 64-bit address boundaries and each 64-bit word may only be programmed once per write/erase cycle.

Applications using Fapi\_issueProgrammingCommand() in Fapi\_AutoEccGeneration or Fapi\_DataAndEcc modes are implicitly performing 64-bit programming since ECC is programmed for each 64 bits. Applications using Fapi\_DataOnly mode with fewer than 64 bits may be impacted by this advisory.

The DCSM OTP programming must be aligned to 128-bit address boundaries and each 128-bit word may only be programmed once. The exceptions are:

- 1. The DCSM Zx-LINKPOINTER1 and Zx-LINKPOINTER2 values in the DCSM OTP should be programmed together, and may be programmed 1 bit at a time as required by the DCSM operation.

- 2. The DCSM Zx-LINKPOINTER3 value in the DCSM OTP may be programmed 1 bit at a time as required by the DCSM operation.

# Workarounds

All applications should follow the restrictions outlined in this advisory. Contact TI for devices already in production which violate this advisory.

# eQEP: Position Counter Incorrectly Reset on Direction Change During Index

#### **Revisions Affected**

B, C

#### **Details**

While using the PCRM = 0 configuration, if the direction change occurs when the index input is active, the position counter (QPOSCNT) could be reset erroneously, resulting in an unexpected change in the counter value. This could result in a change of up to ±4 counts from the expected value of the position counter and lead to unexpected subsequent setting of the error flags.

While using the PCRM = 0 configuration [that is, Position Counter Reset on Index Event (QEPCTL[PCRM] = 00)], if the index event occurs during the forward movement, then the position counter is reset to 0 on the next eQEP clock. If the index event occurs during the reverse movement, then the position counter is reset to the value in the QPOSMAX register on the next eQEP clock. The eQEP peripheral records the occurrence of the first index marker (QEPSTS[FIMF]) and direction on the first index event marker (QEPSTS[FIDF]) in QEPSTS registers. It also remembers the quadrature edge on the first index marker so that same relative quadrature transition is used for index event reset operation.

If the direction change occurs while the index pulse is active, the module would still continue to look for the relative quadrature transition for performing the position counter reset. This results in an unexpected change in the position counter value.

The next index event without a simultaneous direction change will reset the counter properly and work as expected.

#### Workarounds

Do not use the PCRM = 0 configuration if the direction change could occur while the index is active and the resultant change of the position counter value could affect the application.

Other options for performing position counter reset, if appropriate for the application [such as Index Event Initialization (IEI)], do not have this issue.

#### **Advisory**

#### eQEP: eQEP Inputs in GPIO Asynchronous Mode

# **Revisions Affected**

B, C

# **Details**

If any of the eQEP input pins are configured for GPIO asynchronous input mode via the GPxQSELn registers, the eQEP module may not operate properly because the eQEP peripheral assumes the presence of external synchronization to SYSCLKOUT on inputs to the module. For example, QPOSCNT may not reset or latch properly, and pulses on the input pins may be missed.

For proper operation of the eQEP module, input GPIO pins should be configured via the GPxQSELn registers for synchronous input mode (with or without qualification), which is the default state of the GPxQSEL registers at reset. All existing eQEP peripheral examples supplied by TI also configure the GPIO inputs for synchronous input mode.

The asynchronous mode should not be used for eQEP module input pins.

#### **Workarounds**

Configure GPIO inputs configured as eQEP pins for non-asynchronous mode (any GPxQSELn register option except "11b = Asynchronous").

# HWBIST: Avoiding Spurious Interrupts While Using HWBIST

#### **Revisions Affected**

B, C

#### **Details**

HWBIST has the capability to log interrupts received while the CPU is under test and reissue them after HWBIST completes. Interrupts received in the clock cycle before the interrupt logging is enabled are executed before the HWBIST runs. In the next cycle, when interrupt logging is enabled, interrupts are logged and reissued when the HWBIST completes.

The interrupt events for CPU Timer 1 and CPU Timer 2 are valid for 2 SYSCLK cycles. If the first cycle happens a cycle before interrupt logging is enabled and the second cycle coincides with the enabling of interrupt logging, the interrupt is executed once as expected before the logging (clearing the CPU Timer TCR.TIF flag), but then is logged by the interrupt logger and triggered again after HWBIST completes. Because the TCR.TIF flag was already cleared by the previous ISR, this is an unexpected spurious interrupt.

This is only applicable to the non-PIE CPU Timer interrupts. The CPU Timer 0 interrupt is managed by the PIE and its pulse width is only one SYSCLK cycle.

#### Workarounds

Disable CPU Timer 1 and 2 interrupts before enabling interrupt logging and restore them later. The steps are:

- 1. Clear the timer interrupt enable bit TCR.TIE for CPU Timers 1 and 2.

- 2. Run normal HWBIST sequence: save registers, enable interrupt logging, run HWBIST, restore registers, end interrupt logging.

- 3. Check if the CPU Timers' TCR.TIF flags are set. If the flags are set, set the corresponding CPU IFR bit to trigger the interrupt.

- 4. Restore TCR.TIE.

# PLL: May Not Lock on the First Lock Attempt

#### **Revisions Affected**

B, C

#### **Details**

The PLL may not start properly at device power up or wake up from Hibernate. The PLLSTS[LOCKS] bit is set, but the PLL does not produce a clock.

Once the PLL has properly started, the PLL can be disabled and reenabled with no issues and will stay locked. However, the PLL lock problem could reoccur on a subsequent power-up or Hibernate cycle.

If the SYSPLL has not properly started and is selected as the CPU clock source, the CPU will stop executing instructions. The occurrence rate of this transient issue is low and after an initial occurrence, this issue may not be subsequently observed in the system again. Implementation of the workaround reduces the rate of occurrence.

This advisory applies to both PLLs, with a different workaround for each.

#### **Workarounds**

#### SYSPLL Workaround:

Repeated lock attempts will reduce the likelihood of seeing the condition on the final attempt. TI recommends a minimum of five lock sequences in succession when the PLL is configured the first time after a power up. A lock sequence means disabling the PLL, starting the PLL locking, and waiting for the LOCKS bit to set. After the final sequence, the clock source is switched to use the PLL output as normal.

The Watchdog timer can be used to detect that the condition has occurred because it is not clocked by the PLL output. The Watchdog should be enabled before selecting the PLL as the clock source and configured to reset the device. If the PLL is not producing a clock, the Watchdog will reset the device and the user initialization software will therefore repeat the PLL initialization.

Many applications do not have a different initialization sequence for a Watchdog-initiated reset; for these applications, no further action is required. For applications that do use a different device initialization sequence when a Watchdog reset is detected, a flag can be used to identify the Watchdog reset as a PLL cause. The SYSDBGCTL[BIT\_0] bit (which is bit 0 at 0x0005D12C) can be set active during the PLL lock sequence and used to distinguish a Watchdog PLL retry attempt versus a different Watchdog reset source.

The SYSPLLSTS[SLIPS] should also be checked immediately after setting the PLL as the SYSCLK source with SYSPLLCTL1[PLLCLKEN]. If SLIPS indicates a PLL slip, then the PLL should be disabled and locked again until there are no slips detected.

See the C2000Ware InitSysPII() function for an example implementation of this workaround, as well as the DriverLib function SysCtl setClock().

The workaround can also be applied at the System level by a supervisor resetting the device if it is not responding.

# Advisory (continued) PLL: May Not Lock on the First Lock Attempt

#### **AUXPLL Workaround:**

CPU Timer 2 can be used to detect that the AUXPLL is active before it is used as a clock source for USB. If the AUXPLL is not active, repeat the lock attempt until successful.

The AUXPLLSTS[SLIPS] should also be checked immediately after setting the PLL as the AUXPLLCLK source with AUXPLLCTL1[PLLCLKEN]. If SLIPS indicates a PLL slip, then the PLL should be disabled and locked again until there are no slips detected.

See the C2000Ware InitAuxPII() function for an example implementation of this workaround, as well as the DriverLib function SysCtl setAuxClock().

#### Note

The USB Boot Mode does not implement the previous workarounds. Applications using USB Boot will need to implement any retry attempts at the system level.

#### **Advisory**

# PLL: Power Down and Bypass May Take up to 120 SYSCLK Cycles to be Effective

#### **Revisions Affected**

B, C

#### **Details**

When the PLL is powered down (that is, SYPLLCTL1.PLLEN = 0) or bypassed (that is, SYSPLLCTL1.PLLCLKEN = 0), there is a necessary period of clock synchronization before the PLL bypass completes. During this time, if PLLSYSCLKDIV (or other clock divider) is set to a smaller value, the resulting system clock could be unexpectedly more than the rated device frequency.

Implementing the workaround below will allow the PLL bypass operation to complete before any other code is executed, ensuring expected device frequencies and proper system operation.

#### **Workarounds**

Add a software delay of 120 SYSCLK cycles using a NOP instruction while performing either a PLL power down or a PLL bypass operation.

#### Example:

```

SYSPLLCTL1.PLLCLKEN = 0; // Bypassing the PLL asm(" RPT #120 || NOP"); // Delay of 120 SYSCLK Cycles SYSPLLCTL1.PLLEN = 0; // Powering down the PLL asm(" RPT #120 || NOP"); // Delay of 120 SYSCLK Cycles

```

The latest released C2000Ware, which has this workaround implemented, can be used as reference.

SDFM: Data Filter Output Does Not Saturate at Maximum Value With Sinc3 and OSR = 256

**Revisions Affected**

B. C

**Details**

If the differential input of the Sigma-Delta Filter Module (SDFM) is greater than or equal to +FSR (full-scale differential voltage input range), then the output of the SDFM clips with a stream of ones. When this stream of ones is fed to a data filter that is configured as a sinc3 filter with an OSR = 256, the output of the filter does not saturate at the maximum value (16777215 in 32-bit mode or 32767 in 16-bit mode); but, instead roll over to the minimum value (–16777216 in 32-bit mode or –32768 in 16-bit mode).

**Workarounds**

Maintain the differential input of the SDFM in the specified linear input range as specified in the modulator data sheet.

**Advisory**

SDFM: Spurious Data Acknowledge Event When Data Filter is Configured and Enabled for the First Time

**Revisions Affected**

B, C

**Details**

When the SDFM data filter is configured and enabled for the first time, it is possible to get one spurious data acknowledge event (AFx) before the data filter settles to give correct digital data. Subsequent data acknowledge events (AFx)/DMA events occur correctly as per data filter configuration.

Workarounds

Do the following:

- 1. Configure and enable the SDFM data filter.

- 2. Delay for at least latency of data filter + 5 SD-Cx clock cycles.

- 3. Enable SDFM data acknowledge interrupts/DMA events.

# SDFM: Spurious Data Acknowledge Event When Data Filter is Synchronized Using PWM FILRES Signal

#### **Revisions Affected**

B. C

#### **Details**

When the SDFM data filters are synchronized using the PWM FILRES signal, it is possible to get a spurious data acknowledge event (AFx) before the data filter settles to give correct digital data. Subsequent data acknowledge events (AFx) occur correctly as per data filter configuration before the next PWM FILRES signal.

#### Workarounds

Do the following:

- 1. Choose any PWMx to work in the same time base as the PWM that generates the FILRES pulse.

- PWMx should also interrupt the CPU/CLA at least 1.2 μs after the PWM FILRES

pulse gets applied in order to clear the SDIFLG register that may be set because of

the spurious data acknowledge event.

- 3. SDFM CPUISR or SDFM CLATask:

- a. Collect the required number of samples, N, after the FILRES pulse.

- b. If the number of samples is less than or equal to N, clear the SDIFLG register; otherwise, do not clear the SDIFLG register to prevent further SDFM interrupts.

# **Advisory**

SDFM: Comparator Filter Module may Generate Spurious Over-Value and Under-Value Conditions

#### **Revisions Affected**

B, C

#### **Details**

When interrupts are enabled in the SDFM comparator module, it may trigger spurious over-value (SDIFLG.IEHx, x = 1 to 4) or under-value (SDIFLG.IELx, x = 1 to 4) conditions. These are depicted as IELx and IEHx interrupt outputs in the "Block Diagram of One Filter Module" figure in the TMS320F2837xS Real-Time Microcontrollers Technical Reference Manual.

#### **Workarounds**

These erroneous interrupts can be eliminated by implementing the following workaround:

- Comparator OSR (COSR) value should be greater than or equal to 5.

- After changing COSR, wait for at least latency of comparator filter and 5 SD-Cx cycles before enabling comparator interrupts SDCPARMx.IEH and SDCPARMx.IEL.

# SDFM: Dynamically Changing Threshold Settings (LLT, HLT), Filter Type, or COSR Settings Will Trigger Spurious Comparator Events

#### **Revisions Affected**

B, C

#### **Details**

When SDFM comparator settings—such as filter type, lower/upper threshold, or comparator OSR (COSR) settings—are dynamically changed during run time, spurious comparator events will be triggered. The spurious comparator event will trigger a corresponding CPU interrupt, CLA task, ePWM X-BAR events, and GPIO output X-BAR events if configured appropriately.

#### Workarounds

When comparator settings need to be changed dynamically, follow the procedure below to ensure spurious comparator events do not generate a CPU interrupt or CLA task:

- 1. Disable the SDFM comparator interrupt.

- 2. Change comparator settings such as lower/upper threshold, filter type, or COSR.

- 3. COSR value should be greater than or equal to 5.

- 4. Delay for at least a latency of comparator filter + 5 SD-Cx clock cycles.

- 5. Enable the SDFM comparator interrupt.

When comparator settings need to be changed dynamically, follow the procedure below to ensure spurious comparator events do not trigger X-BAR events (ePWM X-BAR and GPIO output X-BAR events):

- Disable the SDFM X-BAR trip events in the corresponding X-BAR registers (ePWM X-BAR or GPIO X-BAR event).

- 2. Change comparator settings such as lower/upper threshold, filter type, or COSR.

- 3. COSR value should be greater than or equal to 5.

- 4. Delay for at least a latency of comparator filter + 5 SD-Cx clock cycles.

- 5. Enable the SDFM X-BAR trip events in the corresponding X-BAR registers (ePWM X-BAR or GPIO X-BAR event).

#### **Advisory**

SDFM: Dynamically Changing Data Filter Settings (Such as Filter Type or DOSR) Will Trigger Spurious Data Acknowledge Events

#### **Revisions Affected**

B, C

#### **Details**

When SDFM data settings—such as filter type or DOSR settings—are dynamically changed during run time, spurious data-filter-ready events will be triggered. The spurious data-ready event will trigger a corresponding CPU interrupt, CLA task, and DMA trigger if configured appropriately.

#### Workarounds

When SDFM data filter settings need to be changed dynamically, follow the procedure below to ensure spurious data-filter-ready events are not generated:

- 1. Disable the SDFM data filter.

- 2. Change SDFM data filter settings such as filter type or DOSR.

- 3. Delay for at least a latency of data filter + 5 SD-Cx clock cycles.

- 4. Enable the SDFM data filter.

# SDFM: Manchester Mode (Mode 2) Does Not Produce Correct Filter Results Under Several Conditions

#### **Revisions Affected**

B. C

#### **Details**

The Manchester decoding algorithm samples the Manchester bitstream with SYSCLK in a calibration window of 1024 SDx\_Dy signal transitions. The derived clock from the Manchester bitstream is used to sample for data in the subsequent calibration window cycle.

There are several scenarios that can cause large errors in the filter results:

- Any single noise event on SDx\_Dy can corrupt the decoded Manchester clock and cause subsequent data to be sampled at an incorrect frequency.

- If the Manchester bitstream clock rate is a near exact integer multiple of SYSCLK, then an occasional Manchester bit can be skipped when the phases of the Manchester stream and internal SYSCLK drift past each other in phase before the next 1024 transition calibration window becomes effective. Deviations in duty cycle from 50% of the Manchester clock also need to be accounted for to ensure the longer Manchester pulses are not an integer multiple of SYSCLK. This situation can be unavoidable if the clock sources for either the SD modulator or this device have a wide variation since a wide range of keep out frequencies become problematic

- If the Manchester edge delay variation between rising and falling (duty cycle of the bitstream) is greater than one SYSCLK, then the SDFM clock decode algorithm can incorrectly identify the clock period as shorter than it is.

#### Workarounds

The workarounds available are:

- Avoid using Manchester mode and consider using Mode 0, which provides the best filter performance under noisy conditions. This is the recommended workaround.

- Avoid any noise on the Manchester bitstream and avoid integer multiples of SYSCLK for the selected Manchester clock source. A precision clock source for the modulator and this device must be used.

- Ensure rising and falling edge delays (high and low pulses) are within one SYSCLK of each other in length.

- Design an application-level algorithm that is robust against occasional incorrect SDFM results.

# FPU: FPU-to-CPU Register Move Operation Preceded by Any FPU 2p Operation

#### **Revisions Affected**

B, C

#### **Details**

This advisory applies when a multicycle (2p) FPU instruction is followed by a FPU-to-CPU register transfer. If the FPU-to-CPU read instruction source register is the same as the 2p instruction destination, then the read may be of the value of the FPU register before the 2p instruction completes. This occurs because the 2p instructions rely on data-forwarding of the result during the E3 phase of the pipeline. If a pipeline stall happens to occur in the E3 phase, the result does not get forwarded in time for the read instruction.

The 2p instructions impacted by this advisory are MPYF32, ADDF32, SUBF32, and MACF32. The destination of the FPU register read must be a CPU register (ACC, P, T, XAR0...XAR7). This advisory does not apply if the register read is a FPU-to-FPU register transfer.

In the example below, the 2p instruction, MPYF32, uses R6H as its destination. The FPU register read, MOV32, uses the same register, R6H, as its source, and a CPU register as the destination. If a stall occurs in the E3 pipeline phase, then MOV32 will read the value of R6H before the MPYF32 instruction completes.

# **Example of Problem:**

```

MPYF32 R6H, R5H, R0H ; 2p FPU instruction that writes to R6H

|| MOV32 *XAR7++, R4H

F32TOUI16R R3H, R4H ; delay slot

ADDF32 R2H, R2H, R0H

|| MOV32 *--SP, R2H ; alignment cycle

MOV32 @XAR3, R6H ; FPU register read of R6H

```

Figure 3-1 shows the pipeline diagram of the issue when there are no stalls in the pipeline.

|    | Instruction          | F1 | F2            | D1 | D2 | R1    | R2 | Е  | w  |           | Comments                                                                                                                                                                                                                                                |  |

|----|----------------------|----|---------------|----|----|-------|----|----|----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|    |                      | -  | FPU pipeline> |    | R1 | R1 R2 |    | E2 | E3 | Comments  |                                                                                                                                                                                                                                                         |  |

| 11 | MPYF32 R6H, R5H, R0H | т1 |               |    |    |       |    |    |    |           |                                                                                                                                                                                                                                                         |  |

|    | MOV32 *XAR7++, R4H   |    |               |    |    |       |    |    |    |           |                                                                                                                                                                                                                                                         |  |

| 12 | F32TOUI16R R3H, R4H  | 12 | 11            |    |    |       |    |    |    |           |                                                                                                                                                                                                                                                         |  |

| 13 | ADDF32 R3H, R2H, R0H | 13 | 12            | 11 |    |       |    |    |    |           |                                                                                                                                                                                                                                                         |  |

| 13 | MOV32 *SP, R2H       | 13 | 12            | 11 |    |       |    |    |    |           |                                                                                                                                                                                                                                                         |  |

| I4 | MOV32 @XAR3, R6H     | I4 | 13            | 12 | 11 |       |    |    |    |           |                                                                                                                                                                                                                                                         |  |

|    |                      |    | I4            | 13 | 12 | 11    |    |    |    |           |                                                                                                                                                                                                                                                         |  |

|    |                      |    |               | I4 | 13 | 12    | I1 |    |    |           |                                                                                                                                                                                                                                                         |  |

|    |                      |    |               |    | I4 | 13    | I2 | I1 |    |           |                                                                                                                                                                                                                                                         |  |

|    |                      |    |               |    |    | Ι4    | I3 | I2 | I1 |           |                                                                                                                                                                                                                                                         |  |

|    |                      |    |               |    |    |       | 14 | 13 | 12 | <u>11</u> | 14 samples the result as it enters the R2 phase. The product R6H=R5H*R0H (II) finishes computing in the E3 phase, but is <b>forwarded</b> as an operand to I4. This makes I4 appear to be a 2p instruction, but I4 actually takes 3p cycles to compute. |  |

|    |                      |    |               |    |    |       |    | I4 | 13 | 12        |                                                                                                                                                                                                                                                         |  |

|    |                      |    |               |    |    |       |    |    | I4 | 13        |                                                                                                                                                                                                                                                         |  |

Figure 3-1. Pipeline Diagram of the Issue When There are no Stalls in the Pipeline

# Advisory (continued) FPU: FPU-to-CPU Register Move Operation Preceded by Any FPU 2p Operation

Figure 3-2 shows the pipeline diagram of the issue if there is a stall in the E3 slot of the instruction I1.

|    | Instruction                                   | F1            | F2 | D1 | D2 | R1 | R2 | E  | w        |               | Comments                                                                                                                                                                                                                   |

|----|-----------------------------------------------|---------------|----|----|----|----|----|----|----------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                               | FPU pipeline> |    | R1 | R2 | E1 | E2 | E3 | Comments |               |                                                                                                                                                                                                                            |

| I1 | MPYF32 R6H, R5H, R0H<br>   MOV32 *XAR7++, R4H | 11            |    |    |    |    |    |    |          |               |                                                                                                                                                                                                                            |

| I2 | F32TOUI16R R3H, R4H                           | 12            | I1 |    |    |    |    |    |          |               |                                                                                                                                                                                                                            |

| 13 | ADDF32 R3H, R2H, R0H                          | 13            | 12 | Il |    |    |    |    |          |               |                                                                                                                                                                                                                            |

| I4 | MOV32 @XAR3, R6H                              | I4            | I3 | I2 | I1 |    |    |    |          |               |                                                                                                                                                                                                                            |

|    |                                               |               | I4 | I3 | I2 | I1 |    |    |          |               |                                                                                                                                                                                                                            |

|    |                                               |               |    | I4 | I3 | 12 | I1 |    |          |               |                                                                                                                                                                                                                            |

|    |                                               |               |    |    | I4 | 13 | I2 | I1 |          |               |                                                                                                                                                                                                                            |

|    |                                               |               |    |    |    | I4 | I3 | I2 | I1       |               |                                                                                                                                                                                                                            |

|    |                                               |               |    |    |    |    | 14 | 13 | I2       | I1<br>(STALL) | I4 samples the result as it enters the R2 phase, but I1 is stalled in E3 and is unable to forward the product of R5H*ROH to I4 (R6H does not have the product yet due to a design bug). So, I4 reads the old value of R6H. |

|    |                                               |               |    |    |    |    | 14 | 13 | I2       |               | There is no change in the pipeline as it was stalled in the previous cycle. I4 had already sampled the old value of R6H in the previous cycle.                                                                             |

|    |                                               |               |    |    |    |    |    | I4 | 13       | 12            | Stall over                                                                                                                                                                                                                 |

Figure 3-2. Pipeline Diagram of the Issue if There is a Stall in the E3 Slot of the Instruction I1

#### Workarounds

Treat MPYF32, ADDF32, SUBF32, and MACF32 in this scenario as 3p-cycle instructions. Three NOPs or non-conflicting instructions must be placed in the delay slot of the instruction.

The C28x Code Generation Tools v.6.2.0 and later will both generate the correct instruction sequence and detect the error in assembly code. In previous versions, v6.0.5 (for the 6.0.x branch) and v.6.1.2 (for the 6.1.x branch), the compiler will generate the correct instruction sequence but the assembler will not detect the error in assembly code.

# **Example of Workaround:**

Figure 3-3 shows the pipeline diagram with the workaround in place.

# Advisory (continued) FPU: FPU-to-CPU Register Move Operation Preceded by Any FPU 2p Operation

|    | Instruction                                   | F1 | F2      | D1     | D2 | R1 | R2 | Е  | w  |               |                                                                                                                                              |

|----|-----------------------------------------------|----|---------|--------|----|----|----|----|----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                               |    | FPU pip | eline> | •  | R1 | R2 | E1 | E2 | E3            | Comments                                                                                                                                     |

| I1 | MPYF32 R6H, R5H, R0H<br>   MOV32 *XAR7++, R4H | 11 |         |        |    |    |    |    |    |               |                                                                                                                                              |

| 12 | F32TOUI16R R3H, R4H                           | 12 | 11      |        |    |    |    |    |    |               |                                                                                                                                              |

| 13 | ADDF32 R3H, R2H, R0H                          | 13 | I2      | 11     |    |    |    |    |    |               |                                                                                                                                              |

| I4 | NOP                                           | I4 | 13      | 12     | I1 |    |    |    |    |               |                                                                                                                                              |

| I5 | MOV32 @XAR3, R6H                              | I5 | I4      | 13     | 12 | I1 |    |    |    |               |                                                                                                                                              |

|    |                                               |    | I5      | I4     | 13 | 12 | I1 |    |    |               |                                                                                                                                              |

|    |                                               |    |         | I5     | I4 | I3 | I2 | I1 |    |               |                                                                                                                                              |

|    |                                               |    |         |        | I5 | I4 | 13 | I2 | I1 |               |                                                                                                                                              |

|    |                                               |    |         |        |    | 15 | 14 | 13 | 12 | I1<br>(STALL) | Due to one extra NOP, I5 does not<br>reach R2 when I1 enters E3; thus,<br>forwarding is not needed.                                          |

|    |                                               |    |         |        |    | 15 | I4 | 13 | 12 | I1            | There is no change due to the stall in the previous cycle.                                                                                   |

|    |                                               |    |         |        |    |    | 15 | 14 | 13 | 12            | Il moves out of E3 and I5 moves to R2. R6H has the result of R5H*R0H and is read by I5. There is no need to forward the result in this case. |

|    |                                               |    |         |        |    |    |    | 15 | Ι4 | 13            |                                                                                                                                              |

Figure 3-3. Pipeline Diagram With Workaround in Place

# FPU: LUF, LVF Flags are Invalid for the EINVF32 and EISQRTF32 Instructions

#### **Revisions Affected**

B, C

#### **Details**

This advisory applies to the EINVF32 and EISQRTF32 instructions. The expected results for these instructions are correct; however, the underflow (LUF) and overflow (LVF) flags are not. These flags are invalid and should not be used.

The LUF and LVF flags are not accessible using C code, so the overall impact of this advisory is expected to be small. If the user chooses to use these flags (for example, when coding a time-critical algorithm) in assembly as part of a mixed C/ASM project, the user will need to disable interrupts around the assembly code using the flags, and also preserve the flags through any use of EINVF32 or EISQRTF32 instructions.

#### Workarounds

There is no workaround for using these flags in C code, and they should be considered invalid for the reasons presented under **NOTES ON COMPILER AND TOOLS USAGE**.

The workaround shown here provides a way to preserve the LVF, LUF flags across the use of EISQRTF32 and EINVF32 in assembly-only code.

Do not rely on the LUF and LVF flags to catch underflow/overflow conditions resulting from the EINVF32 and EISQRTF32 instructions. Instead, check the operands for the following conditions (in code) before using each instruction:

EINVF32 Divide by 0

EISQRTF32 Divide by 0, Divide by a negative input

Disregard the contents of the LUF and LVF flags by saving the flags to the stack before calling the instruction, and subsequently restoring the values of the flags once the instruction completes.

MOV32 \*SP++,STF ; Save off current status flags ; Execute operation

NOP ; Wait for operations to complete MOV32 STF,\*--SP ; Restore previous status flags

If the PIE interrupts are tied to the LUF and LVF flags, disable the interrupts (at the PIE) before using either the EINVF32 or EISQRTF32 instruction. Check to see if the LUF and LVF flags are set; if they are, a variable can be set to indicate that a false LUF/LVF condition is detected. Clear the flags in the STF (FPU status flag) before re-enabling the interrupts.

Once the interrupts are reenabled at the PIE, the interrupt may occur (if the LUF/LVF interrupt lines were asserted by either of the two instructions) and execution branches to the Interrupt Service Routine (ISR). Check the flag to determine if a false condition has occurred; if it has, disregard the interrupt.

Do not clear the PIE IFR bits (that latch the LUF and LVF flags) directly because an interrupt event on the same PIE group (PIE group 12) may inadvertently be missed.

# Advisory (continued) FPU: LUF, LVF Flags are Invalid for the EINVF32 and EISQRTF32 Instructions

Here is an example:

```

_flag_LVFLUF_set

.usect ".ebss",2,1,1

MOV32

; Save off current status flags

*SP++,STF

; Load the PieCtrlRegs page to the DP

DP, #_PieCtrlRegs.PIEIER12.all

MOVW

; Zero out PIEIER12.7/8, i.e. disable LUF/LVF interrupts

@_PieCtrlRegs.PIEIER12.all, #0xFF3F

EISQRTF32/EINVF32

Execute operation

XAR3, #_flag_LVFLUF_set

*+XAR3[0], STF

*+XAR3[0], #0x3

Wait for operation to complete save STF to _flag_LVFLUF_set

MOVL

MOV32

AND

mask everything but LUF/LVF

; Clear Latched overflow, underflow flag

SETFLG LUF=0, LVF=0

; Re-enable PIEIER12.7/8, i.e. re-enable the LUF/LVF interrupts

@_PieCtrlRegs.PIEIER12.all, #0x00C0

OR

MOV32

STF,*--SP

; Restore previous status flags

```

#### In the ISR,

```

__interrupt void fpu32_luf_lvf_isr (void) {

// Check the flag for whether the LUF, LVF flags set by

// either EISRTF32 or EINVF32

if((flag_LVFLUF_set & 0x3U) != 0U)

{

//Reset flag

flag_LVFLUF_set = 0u;

// Do Nothing

else

//If flag_LVFLUF_set was not set then this interrupt

// is the legitimate result of an overflow/underflow

// from an FPU operation (not EISQRTF32/EINVF32)

// Handle Overflow/Underflow condition

. . .

. . .

. . .

// Ack the interrupt and exit

```

# Advisory (continued) FPU: LUF, LVF Flags are Invalid for the EINVF32 and EISQRTF32 Instructions

#### Note

# NOTES ON COMPILER AND TOOLS USAGE

The compiler does not use LVF/LUF as condition codes for conditional instructions and neither does the Run Time Support (RTS) Library test LVF/LUF in any way.

The compiler may generate code that modifies LVF/LUF, meaning the value of the STF register (that contain these flags) is undefined at function boundaries. Thus, although the sqrt routine in the library may cause LVF/LUF to be set, there is no assurance in the CGT that the user can read these bits after sqrt returns.

Although the compiler does provide the \_\_eisqrtf and \_\_einvf32 intrinsics, it does not provide an intrinsic to read the LVF/LUF bits or the STF register. Thus, the user has no way to access these bits from C code.

The use of inline assembly code to read the STF register is unreliable and is discouraged. The workaround presented in the Workarounds section is applicable to assembly code that uses the EISQRTF32 and EINVF32 instructions and does not call any compiler-generated code. For C code, the user must consider these flags to be unreliable, and therefore, neither poll these flags in code nor trigger interrupts off of them.

# Memory: Prefetching Beyond Valid Memory

#### **Revisions Affected**

B, C

#### **Details**