# TMS320DM644x DMSoC Inter-Integrated Circuit (I2C) Peripheral

# **User's Guide**

Literature Number: SPRUE27F March 2011

| Pref | face      |                                                 | . 6 |

|------|-----------|-------------------------------------------------|-----|

| 1    | Introdu   | ction                                           | 8   |

|      | 1.1       | Purpose of the Peripheral                       | . 8 |

|      | 1.2       | Features                                        | 8   |

|      | 1.3       | Functional Block Diagram                        | . 9 |

|      | 1.4       | Industry Standard(s) Compliance Statement       | . 9 |

| 2    | Periphe   | eral Architecture                               | 10  |

|      | 2.1       | Bus Structure                                   | 10  |

|      | 2.2       | Clock Generation                                | 11  |

|      | 2.3       | Clock Synchronization                           | 12  |

|      | 2.4       | Signal Descriptions                             | 12  |

|      | 2.5       | START and STOP Conditions                       | 13  |

|      | 2.6       | Serial Data Formats                             | 14  |

|      | 2.7       | Operating Modes                                 | 16  |

|      | 2.8       | NACK Bit Generation                             | 17  |

|      | 2.9       | Arbitration                                     | 18  |

|      | 2.10      | Reset Considerations                            | 19  |

|      | 2.11      | Initialization                                  | 19  |

|      | 2.12      | Interrupt Support                               | 22  |

|      | 2.13      | DMA Events Generated by the I2C Peripheral      | 22  |

|      | 2.14      | Power Management                                | 23  |

|      | 2.15      | Emulation Considerations                        | 23  |

| 3    | Registe   | ers                                             | 23  |

|      | 3.1       | I2C Own Address Register (ICOAR)                | 24  |

|      | 3.2       | I2C Interrupt Mask Register (ICIMR)             | 25  |

|      | 3.3       | I2C Interrupt Status Register (ICSTR)           | 26  |

|      | 3.4       | I2C Clock Divider Registers (ICCLKL and ICCLKH) | 29  |

|      | 3.5       | I2C Data Count Register (ICCNT)                 | 30  |

|      | 3.6       | I2C Data Receive Register (ICDRR)               | 31  |

|      | 3.7       | I2C Slave Address Register (ICSAR)              | 31  |

|      | 3.8       | I2C Data Transmit Register (ICDXR)              | 32  |

|      | 3.9       | I2C Mode Register (ICMDR)                       | 33  |

|      | 3.10      | I2C Interrupt Vector Register (ICIVR)           | 37  |

|      | 3.11      | I2C Extended Mode Register (ICEMDR)             | 38  |

|      | 3.12      | I2C Prescaler Register (ICPSC)                  |     |

|      | 3.13      | I2C Peripheral Identification Register (ICPID1) | 39  |

|      | 3.14      | I2C Peripheral Identification Register (ICPID2) | 39  |

| ۸nn  | andiy A E | Pavisian History                                | 40  |

# **List of Figures**

| 1  | I2C Peripheral Block Diagram                                                                                         | 9  |

|----|----------------------------------------------------------------------------------------------------------------------|----|

| 2  | Multiple I2C Modules Connected                                                                                       | 10 |

| 3  | Clocking Diagram for the I2C Peripheral                                                                              | 11 |

| 4  | Synchronization of Two I2C Clock Generators During Arbitration                                                       | 12 |

| 5  | Bit Transfer on the I2C-Bus                                                                                          | 13 |

| 6  | I2C Peripheral START and STOP Conditions                                                                             | 13 |

| 7  | I2C Peripheral Data Transfer                                                                                         | 14 |

| 8  | I2C Peripheral 7-Bit Addressing Format (FDF = 0, XA = 0 in ICMDR)                                                    | 14 |

| 9  | I2C Peripheral 10-Bit Addressing Format With Master-Transmitter Writing to Slave-Receiver (FDF = 0, XA = 1 in ICMDR) | 15 |

| 10 | I2C Peripheral Free Data Format (FDF = 1 in ICMDR)                                                                   | 15 |

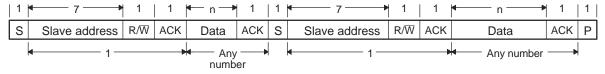

| 11 | I2C Peripheral 7-Bit Addressing Format With Repeated START Condition (FDF = 0, XA = 0 in ICMDR)                      | 15 |

| 12 | Arbitration Procedure Between Two Master-Transmitters                                                                | 18 |

| 13 | I2C Own Address Register (ICOAR)                                                                                     | 24 |

| 14 | I2C Interrupt Mask Register (ICIMR)                                                                                  | 25 |

| 15 | I2C Interrupt Status Register (ICSTR)                                                                                | 26 |

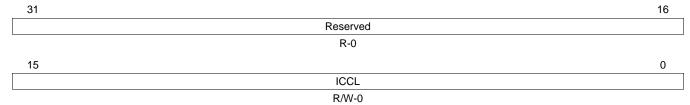

| 16 | I2C Clock Low-Time Divider Register (ICCLKL)                                                                         | 29 |

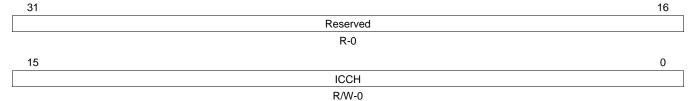

| 17 | I2C Clock High-Time Divider Register (ICCLKH)                                                                        | 29 |

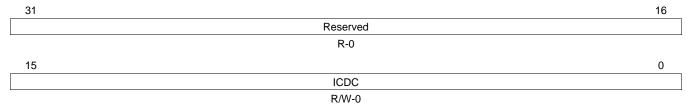

| 18 | I2C Data Count Register (ICCNT)                                                                                      | 30 |

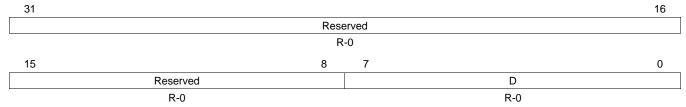

| 19 | I2C Data Receive Register (ICDRR)                                                                                    | 31 |

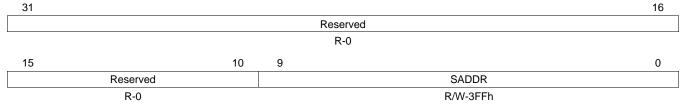

| 20 | I2C Slave Address Register (ICSAR)                                                                                   | 31 |

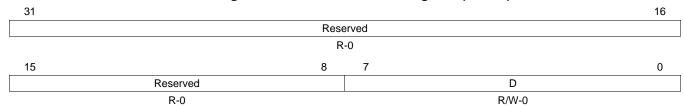

| 21 | I2C Data Transmit Register (ICDXR)                                                                                   | 32 |

| 22 | I2C Mode Register (ICMDR)                                                                                            | 33 |

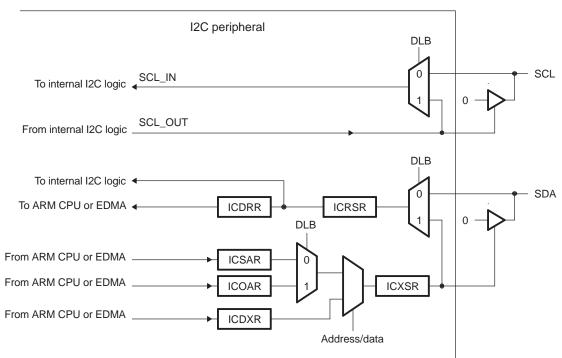

| 23 | Block Diagram Showing the Effects of the Digital Loopback Mode (DLB) Bit                                             | 36 |

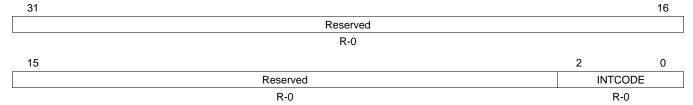

| 24 | I2C Interrupt Vector Register (ICIVR)                                                                                | 37 |

| 25 | I2C Extended Mode Register (ICEMDR)                                                                                  | 38 |

| 26 | I2C Prescaler Register (ICPSC)                                                                                       | 38 |

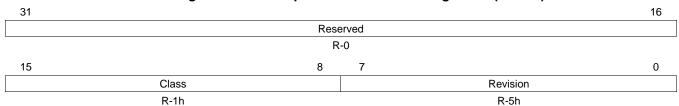

| 27 | I2C Peripheral Identification Register 1 (ICPID1)                                                                    | 39 |

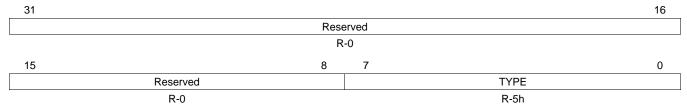

| 28 | I2C Peripheral Identification Register 2 (ICPID2)                                                                    | 39 |

#### www.ti.com

# **List of Tables**

| 1  | Operating Modes of the I2C Peripheral                                     | 16 |

|----|---------------------------------------------------------------------------|----|

| 2  | Ways to Generate a NACK Bit                                               | 17 |

| 3  | Descriptions of the I2C Interrupt Events                                  | 22 |

| 4  | Inter-Integrated Circuit (I2C) Registers                                  | 23 |

| 5  | I2C Own Address Register (ICOAR) Field Descriptions                       | 24 |

| 6  | I2C Interrupt Mask Register (ICIMR) Field Descriptions                    | 25 |

| 7  | I2C Interrupt Status Register (ICSTR) Field Descriptions                  | 26 |

| 8  | I2C Clock Low-Time Divider Register (ICCLKL) Field Descriptions           | 29 |

| 9  | I2C Clock High-Time Divider Register (ICCLKH) Field Descriptions          | 29 |

| 10 | I2C Data Count Register (ICCNT) Field Descriptions                        | 30 |

| 11 | I2C Data Receive Register (ICDRR) Field Descriptions                      | 31 |

| 12 | I2C Slave Address Register (ICSAR) Field Descriptions                     | 31 |

| 13 | I2C Data Transmit Register (ICDXR) Field Descriptions                     | 32 |

| 14 | I2C Mode Register (ICMDR) Field Descriptions                              | 33 |

| 15 | Master-Transmitter/Receiver Bus Activity Defined by RM, STT, and STP Bits | 35 |

| 16 | How the MST and FDF Bits Affect the Role of TRX Bit                       | 36 |

| 17 | I2C Interrupt Vector Register (ICIVR) Field Descriptions                  | 37 |

| 18 | I2C Extended Mode Register (ICEMDR) Field Descriptions                    | 38 |

| 19 | I2C Prescaler Register (ICPSC) Field Descriptions                         | 38 |

| 20 | I2C Peripheral Identification Register 1 (ICPID1) Field Descriptions      | 39 |

| 21 | I2C Peripheral Identification Register 2 (ICPID2) Field Descriptions      | 39 |

| 22 | Document Revision History                                                 | 40 |

# Read This First

#### **About This Manual**

This document describes the inter-integrated circuit (I2C) peripheral in the TMS320DM644x Digital Media System-on-Chip (DMSoC). The I2C peripheral provides an interface between the DMSoC and other devices that are compliant with Philips Semiconductors Inter-IC bus (I2C-bus) specification version 2.1 and connected by way of an I2C-bus. The scope of this document assumes that you are familiar with the I2C-bus specification.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### Related Documentation From Texas Instruments

The following documents describe the TMS320DM644x Digital Media System-on-Chip (DMSoC). Copies of these documents are available on the Internet at <a href="www.ti.com">www.ti.com</a>. Tip: Enter the literature number in the search box provided at <a href="www.ti.com">www.ti.com</a>.

The current documentation that describes the DM644x DMSoC, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: <a href="https://www.ti.com/c6000">www.ti.com/c6000</a>.

- SPRUE14 TMS320DM644x DMSoC ARM Subsystem Reference Guide. Describes the ARM subsystem in the TMS320DM644x Digital Media System-on-Chip (DMSoC). The ARM subsystem is designed to give the ARM926EJ-S (ARM9) master control of the device. In general, the ARM is responsible for configuration and control of the device; including the DSP subsystem, the video processing subsystem, and a majority of the peripherals and external memories.

- <u>SPRUE15</u> *TMS320DM644x DMSoC DSP Subsystem Reference Guide.* Describes the digital signal processor (DSP) subsystem in the TMS320DM644x Digital Media System-on-Chip (DMSoC).

- SPRUE19 TMS320DM644x DMSoC Peripherals Overview Reference Guide. Provides an overview and briefly describes the peripherals available on the TMS320DM644x Digital Media System-on-Chip (DMSoC).

- SPRAA84 TMS320C64x to TMS320C64x+ CPU Migration Guide. Describes migrating from the Texas Instruments TMS320C64x digital signal processor (DSP) to the TMS320C64x+ DSP. The objective of this document is to indicate differences between the two cores. Functionality in the devices that is identical is not included.

- SPRU732 TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide. Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C64x and TMS320C64x+ digital signal processors (DSPs) of the TMS320C6000 DSP family. The C64x/C64x+ DSP generation comprises fixed-point devices in the C6000 DSP platform. The C64x+ DSP is an enhancement of the C64x DSP with added functionality and an expanded instruction set.

www.ti.com Notational Conventions

SPRU871 — TMS320C64x+ DSP Megamodule Reference Guide. Describes the TMS320C64x+ digital signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access (IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.

SPRAAA6 — EDMA v3.0 (EDMA3) Migration Guide for TMS320DM644x DMSoC. Describes migrating from the Texas Instruments TMS320C64x digital signal processor (DSP) enhanced direct memory access (EDMA2) to the TMS320DM644x Digital Media System-on-Chip (DMSoC) EDMA3. This document summarizes the key differences between the EDMA3 and the EDMA2 and provides guidance for migrating from EDMA2 to EDMA3.

# Inter-Integrated Circuit (I2C) Peripheral

#### 1 Introduction

This document describes the operation of the inter-integrated circuit (I2C) peripheral in the TMS320DM644x Digital Media System-on-Chip (DMSoC). The scope of this document assumes that you are familiar with the Philips Semiconductors Inter-IC bus (I2C-bus) specification version 2.1.

#### 1.1 Purpose of the Peripheral

The I2C peripheral provides an interface between the DMSoC and other devices that are compliant with the I2C-bus specification and connected by way of an I2C-bus. External components that are attached to this two-wire serial bus can transmit and receive data that is up to eight bits wide both to and from the DMSoC through the I2C peripheral.

#### 1.2 Features

The I2C peripheral has the following features:

- Compliance with the Philips Semiconductors I2C-bus specification (version 2.1):

- Support for byte format transfer

- 7-bit and 10-bit addressing modes

- General call

- START byte mode

- Support for multiple master-transmitters and slave-receivers mode

- Support for multiple slave-transmitters and master-receivers mode

- Combined master transmit/receive and receive/transmit mode

- I2C data transfer rate of from 10 kbps up to 400 kbps (Philips I2C rate)

- 2 to 8 bit format transfer

- Free data format mode

- One read DMA event and one write DMA event that the DMA can use

- Seven interrupts that the CPU can use

- · Peripheral enable/disable capability

#### 1.2.1 Features Not Supported

- High-speed mode

- · CBUS-compatibility mode

- The combined format in 10-bit addressing mode (the I2C sends the slave address the second byte every time it sends the slave address the first byte).

www.ti.com Introduction

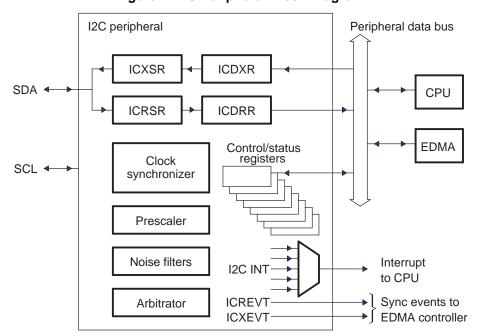

#### 1.3 Functional Block Diagram

A block diagram of the I2C peripheral is shown in Figure 1. Refer to Section 2 for detailed information about the architecture of the I2C peripheral.

Figure 1. I2C Peripheral Block Diagram

#### 1.4 Industry Standard(s) Compliance Statement

The I2C peripheral is compliant with the Philips Semiconductors Inter-IC bus (I2C-bus) specification version 2.1.

Peripheral Architecture www.ti.com

#### 2 Peripheral Architecture

The I2C peripheral consists of the following primary blocks:

- A serial interface: one data pin (SDA) and one clock pin (SCL)

- Data registers to temporarily hold receive data and transmit data traveling between the SDA pin and the CPU or the EDMA controller

- · Control and status registers

- A peripheral data bus interface to enable the CPU and the EDMA controller to access the I2C peripheral registers

- A clock synchronizer to synchronize the I2C input clock (from the processor clock generator) and the clock on the SCL pin, and to synchronize data transfers with masters of different clock speeds

- A prescaler to divide down the input clock that is driven to the I2C peripheral

- A noise filter on each of the two pins, SDA and SCL

- An arbitrator to handle arbitration between the I2C peripheral (when it is a master) and another master

- Interrupt generation logic, so that an interrupt can be sent to the CPU

- EDMA event generation logic, so that activity in the EDMA controller can be synchronized to data reception and data transmission in the I2C peripheral

Figure 1 shows the four registers used for transmission and reception. The CPU or the EDMA controller writes data for transmission to ICDXR and reads received data from ICDRR. When the I2C peripheral is configured as a transmitter, data written to ICDXR is copied to ICXSR and shifted out on the SDA pin one bit a time. When the I2C peripheral is configured as a receiver, received data is shifted into ICRSR and then copied to ICDRR.

#### 2.1 Bus Structure

Figure 1 shows how the I2C peripheral is connected to the I2C bus. The I2C bus is a multi-master bus that supports a multi-master mode. This allows more than one device capable of controlling the bus that is connected to it. A unique address recognizes each I2C device. Each I2C device can operate as either transmitter or receiver, depending on the function of the device. Devices that are connected to the I2C bus can be considered a master or slave when performing data transfers, in addition to being a transmitter or receiver.

**NOTE:** A master device is the device that initiates a data transfer on the bus and generates the clock signals to permit that transfer. Any device that is addressed by this master is considered a slave during this transfer.

An example of multiple I2C modules that are connected for a two-way transfer from one device to other devices is shown in Figure 2.

Pull-up resistors

Serial data (SDA)

Serial clock (SCL)

TI device | 12C | 12

Figure 2. Multiple I2C Modules Connected

Submit Documentation Feedback

www.ti.com Peripheral Architecture

#### 2.2 Clock Generation

As shown in Figure 3, PLL1 receives a signal from an external clock source and produces an I2C input clock. A programmable prescaler (IPSC bit in ICPSC) in the I2C module divides down the I2C input clock to produce a prescaled module clock. The prescaled module clock must be operated within the range of 6.7 to 13.3 MHz. The I2C clock dividers divide-down the high (ICCH bit in ICCLKH) and low portions (ICCL bit in ICCLKL) of the prescaled module clock signal to produce the I2C serial clock, which appears on the SCL pin when the I2C module is configured to be a master on the I2C bus.

External input clock PLL1 I2C input clock I2C module Register bits I2C (ICPSC[IPSC]) prescaler Prescaled module clock -MUST be set to 6.7 to 13.3 MHz Prescaled module clock frequency = 12C input clock frequency (IPSC + 1) Register bits I2C clock (ICCLKL[ICCL]), dividers (ICCLKH[ICCH]) I2C serial clock on SCL pin prescaled module clock frequency I2C serial clock frequency = (ICCL + d) + (ICCH + d) Where d depends on IPSC value in ICPSC: To I2C bus IPSC value 0 6 2h-FFh 5

Figure 3. Clocking Diagram for the I2C Peripheral

#### **CAUTION**

Prescaled Module Clock Frequency Range:

The I2C module must be operated with a prescaled module clock frequency of 6.7 to 13.3 MHz. The I2C prescaler register (I2CPSC) must be configured to this frequency range.

Peripheral Architecture www.ti.com

The prescaler (IPSC bit in ICPSC) must only be initialized while the I2C module is in the reset state (IRS = 0 in ICMDR). The prescaled frequency only takes effect when the IRS bit in ICMDR is changed to 1. Changing the IPSC bit in ICPSC while IRS = 1 in ICMDR has no effect. Likewise, you must configure the I2C clock dividers (ICCH bit in ICCLKH and ICCL bit in ICCLKL) while the I2C module is still in reset (IRS = 0 in ICMDR).

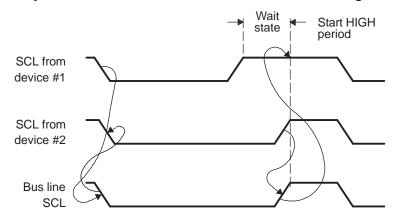

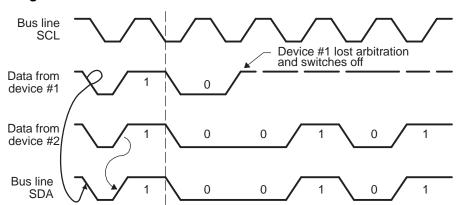

#### 2.3 Clock Synchronization

Only one master device generates the clock signal (SCL) under normal conditions. However, there are two or more masters during the arbitration procedure; and, you must synchronize the clock so that you can compare the data output. Figure 4 illustrates the clock synchronization. The wired-AND property of SCL means that a device that first generates a low period on SCL (device #1) overrules the other devices. At this high-to-low transition, the clock generators of the other devices are forced to start their own low period. The SCL is held low by the device with the longest low period. The other devices that finish their low periods must wait for SCL to be released before starting their high periods. A synchronized signal on SCL is obtained, where the slowest device determines the length of the low period and the fastest device determines the length of the high period.

If a device pulls down the clock line for a longer time, the result is that all clock generators must enter the wait state. This way, a slave slows down a fast master and the slow device creates enough time to store a received data word or to prepare a data word that you are going to transmit.

Figure 4. Synchronization of Two I2C Clock Generators During Arbitration

#### 2.4 Signal Descriptions

The I2C peripheral has a serial data pin (SDA) and a serial clock pin (SCL) for data communication, as shown in Figure 1. These two pins carry information between the DM644x device and other devices that are connected to the I2C-bus. The SDA and SCL pins both are bi-directional. They each must be connected to a positive supply voltage using a pull-up resistor. When the bus is free, both pins are high. The driver of these two pins has an open-drain configuration to perform the required wired-AND function.

See the device-specific data manual for additional timing and electrical specifications for these pins.

#### 2.4.1 Input and Output Voltage Levels

The master device generates one clock pulse for each data bit that is transferred. Due to a variety of different technology devices that can be connected to the I2C-bus, the levels of logic 0 (low) and logic 1 (high) are not fixed and depend on the associated power supply level. See the device-specific data manual for more information.

www.ti.com Peripheral Architecture

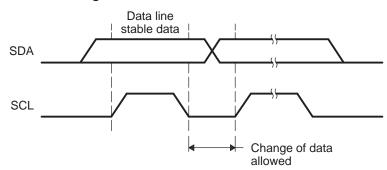

#### 2.4.2 Data Validity

The data on SDA must be stable during the high period of the clock (see Figure 5). The high or low state of the data line, SDA, can change only when the clock signal on SCL is low.

Figure 5. Bit Transfer on the I2C-Bus

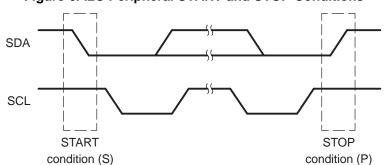

#### 2.5 START and STOP Conditions

The I2C peripheral can generate START and STOP conditions when the peripheral is configured to be a master on the I2C-bus, as shown in Figure 6:

- The START condition is defined as a high-to-low transition on the SDA line while SCL is high. A

master drives this condition to indicate the start of a data transfer.

- The STOP condition is defined as a low-to-high transition on the SDA line while SCL is high. A master

drives this condition to indicate the end of a data transfer.

The I2C-bus is considered busy after a START condition and before a subsequent STOP condition. The bus busy (BB) bit of ICSTR is 1. The bus is considered free between a STOP condition and the next START condition. The BB is 0.

The master mode (MST) bit and the START condition (STT) bit in ICMDR must both be 1 for the I2C peripheral to start a data transfer with a START condition. The STOP condition (STP) bit must be set to 1 for the I2C peripheral to end a data transfer with a STOP condition. A repeated START condition generates when BB is set to 1 and STT is also set to 1. See Section 3.9 for a description of ICMDR (including the MST, STT, and STP bits).

Figure 6. I2C Peripheral START and STOP Conditions

Peripheral Architecture www.ti.com

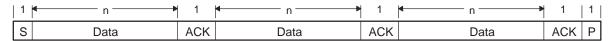

#### 2.6 Serial Data Formats

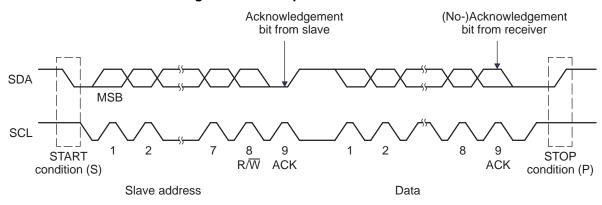

Figure 7 shows an example of a data transfer on the I2C-bus. The I2C peripheral supports 1-bit to 8-bit data values. Figure 7 is shown in an 8-bit data format (BC = 000 in ICMDR). Each bit put on the SDA line is equivalent to one pulse on the SCL line. The data is always transferred with the most-significant bit (MSB) first. The number of data values that can be transmitted or received is unrestricted; however, the transmitters and receivers must agree on the number of data values being transferred.

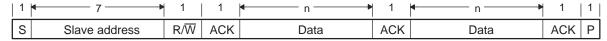

The I2C peripheral supports the following data formats:

- 7-bit addressing mode

- 10-bit addressing mode

- · Free data format mode

Figure 7. I2C Peripheral Data Transfer

#### 2.6.1 7-Bit Addressing Format

In the 7-bit addressing format (Figure 8), the first byte after a START condition (S) consists of a 7-bit slave address followed by a  $R/\overline{W}$  bit. The  $R/\overline{W}$  bit determines the direction of the data.

- $R/\overline{W} = 0$ : The master writes (transmits) data to the addressed slave.

- $R/\overline{W} = 1$ : The master reads (receives) data from the slave.

An extra clock cycle dedicated for acknowledgment (ACK) is inserted after the R/ $\overline{W}$  bit. If the slave inserts the ACK bit, n bits of data from the transmitter (master or slave, depending on the R/ $\overline{W}$  bit) follow it. n is a number from 1 to 8 that the bit count (BC) bits of ICMDR determine. The receiver inserts an ACK bit after the data bits have been transferred.

Write a 0 to the expanded address enable (XA) bit of ICMDR to select the 7-bit addressing format.

Figure 8. I2C Peripheral 7-Bit Addressing Format (FDF = 0, XA = 0 in ICMDR)

n = The number of data bits (from 1 to 8) specified by the bit count (BC) field of ICMDR.

www.ti.com Peripheral Architecture

#### 2.6.2 10-Bit Addressing Format

The 10-bit addressing format (Figure 9) is like the 7-bit addressing format, but the master sends the slave address in two separate byte transfers. The first byte consists of 11110b, the two MSBs of the 10-bit slave address, and  $R/\overline{W} = 0$  (write). The second byte is the remaining 8 bits of the 10-bit slave address. The slave must send acknowledgment (ACK) after each of the two byte transfers. Once the master has written the second byte to the slave, the master can either write data or use a repeated START condition to change the data direction. (For more information about using 10-bit addressing, see the Philips Semiconductors I2C-bus specification.)

Write 1 to the XA bit of ICMDR to select the 10-bit addressing format.

Figure 9. I2C Peripheral 10-Bit Addressing Format With Master-Transmitter Writing to Slave-Receiver (FDF = 0, XA = 1 in ICMDR)

n = The number of data bits (from 1 to 8) specified by the bit count (BC) field of ICMDR.

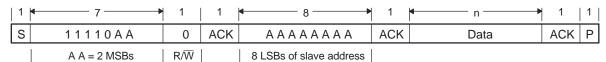

#### 2.6.3 Free Data Format

In the free data format (Figure 10), the first bits after a START condition (S) are a data word. An ACK bit is inserted after each data word, which can be from 1 to 8 bits, depending on the bit count (BC) bits of ICMDR. No address or data-direction bit is sent. Therefore, the transmitter and the receiver must both support the free data format, and the direction of the data must be constant throughout the transfer.

To select the free data format, write 1 to the free data format (FDF) bit of ICMDR.

Figure 10. I2C Peripheral Free Data Format (FDF = 1 in ICMDR)

n = The number of data bits (from 1 to 8) specified by the bit count (BC) field of ICMDR.

#### 2.6.4 Using a Repeated START Condition

The repeated START condition can be used with the 7-bit addressing, 10-bit addressing, and free data formats. The 7-bit addressing format using a repeated START condition (S) is shown in Figure 11. At the end of each data word, the master can drive another START condition. Using this capability, a master can transmit/receive any number of data words before driving a STOP condition. The length of a data word can be from 1 to 8 bits and is selected with the bit count (BC) bits of ICMDR.

Figure 11. I2C Peripheral 7-Bit Addressing Format With Repeated START Condition (FDF = 0, XA = 0 in ICMDR)

n = The number of data bits (from 1 to 8) specified by the bit count (BC) field of ICMDR.

Peripheral Architecture www.ti.com

#### 2.7 Operating Modes

The I2C peripheral has four basic operating modes to support data transfers as a master and as a slave. See Table 1 for the names and descriptions of the modes.

If the I2C peripheral is a master, it begins as a master-transmitter and, typically, transmits an address for a particular slave. When giving data to the slave, the I2C peripheral must remain a master-transmitter. In order to receive data from a slave, the I2C peripheral must be changed to the master-receiver mode.

If the I2C peripheral is a slave, it begins as a slave-receiver and, typically, sends acknowledgment when it recognizes its slave address from a master. If the master will be sending data to the I2C peripheral, the peripheral must remain a slave-receiver. If the master has requested data from the I2C peripheral, the peripheral must be changed to the slave-transmitter mode.

Table 1. Operating Modes of the I2C Peripheral

| Operating Mode          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Slave-receiver mode     | The I2C peripheral is a slave and receives data from a master. All slave modules begin in this mode. In this mode, serial data bits received on SDA are shifted in with the clock pulses that are generated by the master. As a slave, the I2C peripheral does not generate the clock signal, but it can hold SCL low while the intervention of the processor is required (RSFULL = 1 in ICSTR) after data has been received.                                                                                                                                                                                                                                                                                                                                                      |

| Slave-transmitter mode  | The I2C peripheral is a slave and transmits data to a master. This mode can only be entered from the slave-receiver mode; the I2C peripheral must first receive a command from the master. When you are using any of the 7-bit/10-bit addressing formats, the I2C peripheral enters its slave-transmitter mode if the slave address is the same as its own address (in ICOAR) and the master has transmitted $R/\overline{W}=1$ . As a slave-transmitter, the I2C peripheral then shifts the serial data out on SDA with the clock pulses that are generated by the master. While a slave, the I2C peripheral does not generate the clock signal, but it can hold SCL low while the intervention of the processor is required (XSMT = 0 in ICSTR) after data has been transmitted. |

| Master-receiver mode    | The I2C peripheral is a master and receives data from a slave. This mode can only be entered from the master-transmitter mode; the I2C peripheral must first transmit a command to the slave. When you are using any of the 7-bit/10-bit addressing formats, the I2C peripheral enters its master-receiver mode after transmitting the slave address and R/W = 1. Serial data bits on SDA are shifted into the I2C peripheral with the clock pulses generated by the I2C peripheral on SCL. The clock pulses are inhibited and SCL is held low when the intervention of the processor is required (RSFULL = 1 in ICSTR) after data has been received.                                                                                                                              |

| Master-transmitter mode | The I2C peripheral is a master and transmits control information and data to a slave. All master modules begin in this mode. In this mode, data assembled in any of the 7-bit/10-bit addressing formats is shifted out on SDA. The bit shifting is synchronized with the clock pulses generated by the I2C peripheral on SCL. The clock pulses are inhibited and SCL is held low when the intervention of the processor is required (XSMT = 0 in ICSTR) after data has been transmitted.                                                                                                                                                                                                                                                                                           |

www.ti.com Peripheral Architecture

#### 2.8 NACK Bit Generation

When the I2C peripheral is a receiver (master or slave), it can acknowledge or ignore bits sent by the transmitter. To ignore any new bits, the I2C peripheral must send a no-acknowledge (NACK) bit during the acknowledge cycle on the bus. Table 2 summarizes the various ways the I2C peripheral sends a NACK bit.

Table 2. Ways to Generate a NACK Bit

|                                                                    | NACK Bit Generation                                                                                                                                                                                                                       |                                                                                                 |  |  |  |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|

| I2C Peripheral Condition                                           | Basic                                                                                                                                                                                                                                     | Optional                                                                                        |  |  |  |

| Slave-receiver mode                                                | <ul> <li>Disable data transfers (STT = 0 in ICSTR).</li> <li>Allow an overrun condition (RSFULL = 1 in ICSTR).</li> <li>Reset the peripheral (IRS = 0 in ICMDR)</li> </ul>                                                                | Set the NACKMOD bit of ICMDR before the rising edge of the last data bit you intend to receive. |  |  |  |

| Master-receiver mode<br>AND<br>Repeat mode<br>(RM = 1 in ICMDR)    | <ul> <li>Generate a STOP condition (STOP = 1 in ICMDR).</li> <li>Reset the peripheral (IRS = 0 in ICMDR).</li> </ul>                                                                                                                      | Set the NACKMOD bit of ICMDR before the rising edge of the last data bit you intend to receive. |  |  |  |

| Master-receiver mode<br>AND<br>Nonrepeat mode<br>(RM = 0 in ICMDR) | <ul> <li>If STP = 1 in ICMDR, allow the internal data counter to count down to 0 and force a STOP condition.</li> <li>If STP = 0, make STP = 1 to generate a STOP condition.</li> <li>Reset the peripheral (IRS = 0 in ICMDR).</li> </ul> | Set the NACKMOD bit of ICMDR before the rising edge of the last data bit you intend to receive. |  |  |  |

Peripheral Architecture www.ti.com

#### 2.9 Arbitration

If two or more master-transmitters simultaneously start a transmission on the same bus, an arbitration procedure is invoked. The arbitration procedure uses the data presented on the serial data bus (SDA) by the competing transmitters. Figure 12 illustrates the arbitration procedure between two devices. The first master-transmitter, which drives SDA high, is overruled by another master-transmitter that drives SDA low. The arbitration procedure gives priority to the device that transmits the serial data stream with the lowest binary value. Should two or more devices send identical first bytes, arbitration continues on the subsequent bytes.

If the I2C peripheral is the losing master, it switches to the slave-receiver mode, sets the arbitration lost (AL) flag, and generates the arbitration-lost interrupt.

If during a serial transfer the arbitration procedure is still in progress when a repeated START condition or a STOP condition is transmitted to SDA, the master-transmitters involved must send the repeated START condition or the STOP condition at the same position in the format frame. Arbitration is not allowed between:

- A repeated START condition and a data bit

- A STOP condition and a data bit

- A repeated START condition and a STOP condition

Figure 12. Arbitration Procedure Between Two Master-Transmitters

Peripheral Architecture www.ti.com

#### 2.10 Reset Considerations

The I2C peripheral has two reset sources; software reset and hardware reset.

#### 2.10.1 **Software Reset Considerations**

To reset the I2C peripheral, write 0 to the I2C reset (IRS) bit in the I2C mode register (ICMDR). All status bits in the I2C interrupt status register (ICSTR) are forced to their default values, and the I2C peripheral remains disabled until IRS is changed to 1. The SDA and SCL pins are in the high-impedance state.

NOTE: If the IRS bit is cleared to 0 during a transfer, this can cause the I2C bus to hang (SDA and SCL are in the high-impedance state).

#### **Hardware Reset Considerations** 2.10.2

When a hardware reset occurs, all the registers of the I2C peripheral are set to their default values and the I2C peripheral remains disabled until the I2C reset (IRS) bit in the I2C mode register (ICMDR) is changed to 1.

NOTE: The IRS bit must be cleared to 0 while you configure/reconfigure the I2C peripheral. Forcing IRS to 0 can be used to save power and to clear error conditions.

#### 2.11 Initialization

Proper I2C initialization is required prior to starting communication with other I2C device(s). Unless a fully fledged driver is in place, you need to determine the required I2C configuration needed (for example, Master Receiver, etc.) and configure the I2C controller with the desired settings. Enabling the I2C clock should be the first task. Then the I2C controller is placed in reset. You now are ready to configure the I2C controller. Once configuration is done, you need to enable the I2C controller by releasing the controller from reset. Prior to starting communication, you need to make sure that all status bits are cleared and no pending interrupts exist. Once the bus is determined to be available (the bus is not busy), the I2C is ready to proceed with the desired communication.

Peripheral Architecture www.ti.com

#### 2.11.1 Configuring the I2C in Master Receiver Mode and Servicing Receive Data via CPU

The following initialization procedure is for the I2C controller configured in Master Receiver mode. The CPU is used to move data from the I2C receive register to CPU memory (memory accessible by the CPU).

- 1. Enable I2C clock from the Power and Sleep Controller (see the *TMS320DM644x DMSoC ARM Subsystem Reference Guide* (SPRUE14).

- 2. Place I2C in reset (clear IRS = 0 in ICMDR).

- 3. Configure ICMDR:

- Configure I2C as Master (MST = 1).

- Indicate the I2C configuration to be used; for example, Data Receiver (TRX = 0)

- Indicate 7-bit addressing is to be used (XA = 0).

- Disable repeat mode (RM = 0).

- Disable loopback mode (DLB = 0).

- Disable free data format (FDF = 0).

- Optional: Disable start byte mode if addressing a fully fledged I2C device (STB = 0).

- Set number of bits to transfer to be 8 bits (BC = 0).

- Configure Slave Address: the I2C device this I2C master would be addressing (ICSAR = 7BIT ADDRESS).

- 5. Configure the peripheral clock operation frequency (ICPSC). This value should be selected in such a way that the frequency is between 6.7 and 13.3 MHz.

- 6. Configure I2C master clock frequency:

- Configure the low-time divider value (ICCLKL).

- Configure the high-time divider value (ICCLKH).

- 7. Make sure the interrupt status register (ICSTR) is cleared:

- Read ICSTR and write it back (write 1 to clear) ICSTR = ICSTR

- Read ICIVR until it is 0.

- 8. Take I2C controller out of reset: enable I2C controller (set IRS bit = 1 in ICMDR).

- 9. Wait until bus busy bit is cleared (BB = 0 in ICSTR).

- 10. Generate a START event, followed by Slave Address, etc. (set STT = 1 in ICMDR).

- 11. Wait until data is received (ICRRDY = 1 in ICSTR).

- 12. Read data:

- If ICRRDY = 1 in ICSTR, then read ICDRR.

- Perform the previous two steps until receiving one byte short of the entire byte expecting to receive.

- 13. Configure the I2C controller not to generate an ACK on the next/final byte reception: set NACKMOD bit for the I2C to generate a NACK on the last byte received (set NACKMOD = 1 in ICMDR).

- 14. End transfer/release bus when transfer is done. Generate a STOP event (set STP = 1 in ICMDR).

#### 2.11.2 Configuring the I2C in Slave Receiver and Transmitter Mode

The following initialization procedure is for the I2C controller configured in Slave Receiver and Transmitter mode.

- 1. Enable I2C clock from PSC Level. Do this so that you will be able to configure the I2C registers.

- 2. Place I2C in reset (clear IRS = 0 in ICMDR).

- 3. Assign the Address (a 7 bit or 10 bit address) that the I2C Controller will be responding to. This is the Address that the Master is going to broadcast when attempting to start communication with this slave device; I2C Controller.

- If the I2C is able to respond to 7-bit Addressing: Configure XA = 0

- If the I2C is able to respond to 10-bit Addressing: Configure XA = 1

- Program ICOAR = Assigned Address (7-bit or 10-bit Address)

www.ti.com Peripheral Architecture

- 4. Enable the desired interrupt you need to receive by setting the desired interrupt bit field within ICIMR to enable the particular Interrupt.

- AAS = 1; Expect an interrupt when Master's Address matches yours (ICOAR programmed value).

- ICRRDY = 1; Expect a receive interrupt when a byte worth data sent from the master is ready to be read.

- ICXRDY = 1; Expect to receive interrupt when the transmit register is ready to be written with a new data that is to be sent to the master.

- SCD = 1; Expect to receive interrupt when Stop Condition is detected.

- 5. Configure the I2C Controller Operating frequency; this is not the serial clock frequency. This should be between 6.7 and 13.3 MHz. Program IPSC to generate a 6.7 to 13.3 MHz operating frequency.

- Prescaled Module Clock Frequency = PLL1 Output Frequency / (IPSC + 1).

- 6. Configure the I2C Serial Clock Frequency. It is advised to configure this frequency to operate at 400 kHz. This will allow the slave device to be able to attend to all Master speeds. Program ICCH and ICCL.

- 400 kHz = I2C Operating Frequency (6.7 to 13.3 MHz from Step 5) / [(ICCH + 5) + (ICCL + 5)].

- If ICCL == ICCH ≥ 400 kHz = Prescaled Module Clock Frequency / [2 x ICCH + 10]

- 7. Configure the Mode Register.

- MST = 0; Configure the I2C Controller to operate as SLAVE.

- FDF = 0; Free Data Format is disabled.

- BC = 0; Set data width to 8 bytes.

- DLB = 0; Disable Loopback Mode.

- STB = 0; I2C Controller can detect Start condition via hardware.

- RM = 1, STP = 0, STT = 0. See Table 15 (No Activity case).

- Configure remaining bits other than IRS to 0.

- 8. Release I2C from Reset

- IRS = 1; Make sure you do not over write your previous configurations.

- 9. Make sure Interrupt Status Register is cleared.

- ICSTR = ICSTR; Clear Interrupt fields that require writing '1' requirements.

- While (ICIVR != 0) Read ICIVR; Read until it is cleared to 0.

- 10. Instruct I2C Controller to detect START Condition and Its Own Address.

- STT = 1; Make sure you do not over write your previous configurations.

- 11. **MASTER desires to perform a write transfer.** If Master requests a Write, I2C needs to receive data, perform the following:

- Wait for Receive Interrupt to be received, ICRRDY = 1.

- Read Data

- 12. Perform Step 11 until one of the two happens:

- Master generates a STOP Condition (SCD = 1) or

- I2C Slave desires to end receive transfer.

- If the latter, then the I2C needs to Not Acknowledge the last byte to be received from the Master. After reading the byte prior from the last byte set NACKMOD bit so that the I2C automatically NACKs the following received data byte, which is the last data byte.

- NACKMOD = 1; set this field on the 2nd data prior from the last.

- 13. **Master desires to perform a read transfer.** If Master requests a Read, I2C needs to transmit data, perform the following:

- Write Data.

- Wait for Transmit Interrupt to be received, ICXRDY = 1.

- 14. Perform step 13 until a STOP condition is detected (SCD = 1).

Peripheral Architecture www.ti.com

#### 2.12 Interrupt Support

The I2C peripheral is capable of interrupting the ARM CPU. The CPU can determine which I2C events caused the interrupt by reading the I2C interrupt vector register (ICIVR). ICIVR contains a binary-coded interrupt vector type to indicate which interrupt has occurred. Reading ICIVR clears the interrupt flag; if other interrupts are pending, a new interrupt is generated. If there is more than one pending interrupt flag, reading ICIVR clears the highest-priority interrupt flag.

#### 2.12.1 Interrupt Events and Requests

The I2C peripheral can generate the interrupts described in Table 3. Each interrupt has a flag bit in the I2C interrupt status register (ICSTR) and a mask bit in the interrupt mask register (ICIMR). When one of the specified events occurs, its flag bit is set. If the corresponding mask bit is 0, the interrupt request is blocked; if the mask bit is 1, the request is forwarded to the CPU as an I2C interrupt.

Table 3. Descriptions of the I2C Interrupt Events

| I2C Interrupt                                 | Initiating Event                                                                                                                                                                                                                                       |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arbitration-lost interrupt (AL)               | Generated when the I2C arbitration procedure is lost or illegal START/STOP conditions occur                                                                                                                                                            |

| No-acknowledge interrupt (NACK)               | Generated when the master I2C does not receive any acknowledge from the receiver                                                                                                                                                                       |

| Registers-ready-for-access interrupt (ARDY)   | Generated by the I2C when the previously programmed address, data and command have been performed and the status bits have been updated. This interrupt is used to let the controlling processor know that the I2C registers are ready to be accessed. |

| Receive interrupt/status (ICRINT and ICRRDY)  | Generated when the received data in the receive-shift register (ICRSR) has been copied into the ICDRR. The ICRRDY bit can also be polled by the CPU to read the received data in the ICDRR.                                                            |

| Transmit interrupt/status (ICXINT and ICXRDY) | Generated when the transmitted data has been copied from ICDXR to the transmit-shift register (ICXSR) and shifted out on the SDA pin. This bit can also polled by the CPU to write the next transmitted data into the ICDXR.                           |

| Stop-Condition-Detection interrupt (SCD)      | Generated when a STOP condition has been detected                                                                                                                                                                                                      |

| Address-as-Slave interrupt (AAS)              | Generated when the I2C has recognized its own slave address or an address of all (8) zeros.                                                                                                                                                            |

#### 2.12.2 Interrupt Multiplexing

The I2C interrupt to the ARM CPU are not multiplexed with any other interrupt source.

#### 2.13 DMA Events Generated by the I2C Peripheral

For the EDMA controller to handle transmit and receive data, the I2C peripheral generates the following two EDMA events. Activity in EDMA channels can be synchronized to these events.

- Receive event (ICREVT): When receive data has been copied from the receive shift register (ICRSR)

to the data receive register (ICDRR), the I2C peripheral sends an REVT signal to the EDMA controller.

In response, the EDMA controller can read the data from ICDRR.

- Transmit event (ICXEVT): When transmit data has been copied from the data transmit register (ICDXR) to the transmit shift register (ICXSR), the I2C peripheral sends an XEVT signal to the EDMA controller. In response, the EDMA controller can write the next transmit data value to ICDXR.

### 2.14 Power Management

The I2C peripheral can be placed in reduced-power modes to conserve power during periods of low activity. The power management of the I2C peripheral is controlled by the processor Power and Sleep Controller (PSC). The PSC acts as a master controller for power management for all of the peripherals on the device. For detailed information on power management procedures using the PSC, see the TMS320DM644x DMSoC ARM Subsystem Reference Guide (SPRUE14).

#### 2.15 Emulation Considerations

The response of the I2C events to emulation suspend events (such as halts and breakpoints) is controlled by the FREE bit in the I2C mode register (ICMDR). The I2C peripheral either stops exchanging data (FREE = 0) or continues to run (FREE = 1) when an emulation suspend event occurs. How the I2C peripheral terminates data transactions is affected by whether the I2C peripheral is acting as a master or a slave. For more information, see the description of the FREE bit in ICMDR (see Section 3.9).

#### 3 Registers

Table 4 lists the memory-mapped registers for the inter-integrated circuit (I2C) peripheral. See the device-specific data manual for the memory address of these registers. All other register offset addresses not listed in Table 4 should be considered as reserved locations and the register contents should not be modified.

Table 4. Inter-Integrated Circuit (I2C) Registers

| Offset | Acronym | Register Description                     | Section      |

|--------|---------|------------------------------------------|--------------|

| 0h     | ICOAR   | I2C Own Address Register                 | Section 3.1  |

| 4h     | ICIMR   | I2C Interrupt Mask Register              | Section 3.2  |

| 8h     | ICSTR   | I2C Interrupt Status Register            | Section 3.3  |

| Ch     | ICCLKL  | I2C Clock Low-Time Divider Register      | Section 3.4  |

| 10h    | ICCLKH  | I2C Clock High-Time Divider Register     | Section 3.4  |

| 14h    | ICCNT   | I2C Data Count Register                  | Section 3.5  |

| 18h    | ICDRR   | I2C Data Receive Register                | Section 3.6  |

| 1Ch    | ICSAR   | I2C Slave Address Register               | Section 3.7  |

| 20h    | ICDXR   | I2C Data Transmit Register               | Section 3.8  |

| 24h    | ICMDR   | I2C Mode Register                        | Section 3.9  |

| 28h    | ICIVR   | I2C Interrupt Vector Register            | Section 3.10 |

| 2Ch    | ICEMDR  | I2C Extended Mode Register               | Section 3.11 |

| 30h    | ICPSC   | I2C Prescaler Register                   | Section 3.12 |

| 34h    | ICPID1  | I2C Peripheral Identification Register 1 | Section 3.13 |

| 38h    | ICPID2  | I2C Peripheral Identification Register 2 | Section 3.13 |

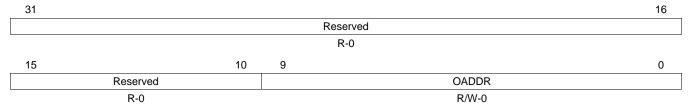

#### 3.1 I2C Own Address Register (ICOAR)

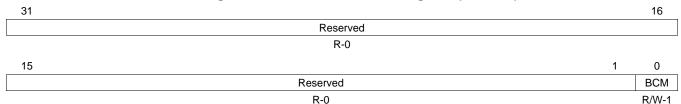

The I2C own address register (ICOAR) is used to specify its own slave address, which distinguishes it from other slaves connected to the I2C-bus. If the 7-bit addressing mode is selected (XA = 0 in ICMDR), only bits 6-0 are used; bits 9-7 are ignored.

The I2C own address register (ICOAR) is shown in Figure 13 and described in Table 5.

#### Figure 13. I2C Own Address Register (ICOAR)

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 5. I2C Own Address Register (ICOAR) Field Descriptions

| Bit   | Field    | Value  | Description                                                                                                            |  |

|-------|----------|--------|------------------------------------------------------------------------------------------------------------------------|--|

| 31-10 | Reserved | 0      | These reserved bit locations are always read as zeros. A value written to this field has no effect.                    |  |

| 9-0   | OADDR    | 0-3FFh | Own slave address. Provides the slave address of the I2C.                                                              |  |

|       |          |        | In 7-bit addressing mode (XA = 0 in ICMDR): bits 6-0 provide the 7-bit slave address of the I2C. Bits 9-7 are ignored. |  |

|       |          |        | In 10-bit addressing mode (XA = 1 in ICMDR): bits 9-0 provide the 10-bit slave address of the I2C.                     |  |

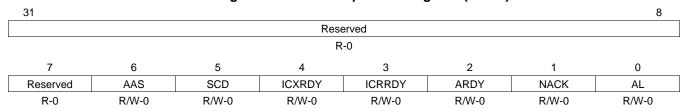

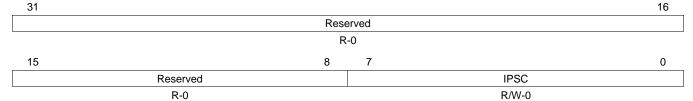

#### 3.2 I2C Interrupt Mask Register (ICIMR)

The I2C interrupt mask register (ICIMR) is used to individually enable or disable I2C interrupt requests. The I2C interrupt mask register (ICIMR) is shown in Figure 14 and described Table 6.

Figure 14. I2C Interrupt Mask Register (ICIMR)

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 6. I2C Interrupt Mask Register (ICIMR) Field Descriptions

| Bit  | Field                                      | Value | Description                                                                                         |

|------|--------------------------------------------|-------|-----------------------------------------------------------------------------------------------------|

| 31-7 | Reserved                                   | 0     | These reserved bit locations are always read as zeros. A value written to this field has no effect. |

| 6    | AAS Address-as-slave interrupt enable bit. |       | Address-as-slave interrupt enable bit.                                                              |

|      |                                            | 0     | Interrupt request is disabled.                                                                      |

|      |                                            | 1     | Interrupt request is enabled.                                                                       |

| 5    | SCD                                        |       | Stop condition detected interrupt enable bit.                                                       |

|      |                                            | 0     | Interrupt request is disabled.                                                                      |

|      |                                            | 1     | Interrupt request is enabled.                                                                       |

| 4    | ICXRDY                                     |       | Transmit-data-ready interrupt enable bit.                                                           |

|      |                                            | 0     | Interrupt request is disabled.                                                                      |

|      |                                            | 1     | Interrupt request is enabled.                                                                       |

| 3    | ICRRDY                                     |       | Receive-data-ready interrupt enable bit.                                                            |

|      |                                            | 0     | Interrupt request is disabled.                                                                      |

|      |                                            | 1     | Interrupt request is enabled.                                                                       |

| 2    | ARDY                                       |       | Register-access-ready interrupt enable bit.                                                         |

|      |                                            | 0     | Interrupt request is disabled.                                                                      |

|      |                                            | 1     | Interrupt request is enabled.                                                                       |

| 1    | NACK                                       |       | No-acknowledgment interrupt enable bit.                                                             |

|      |                                            | 0     | Interrupt request is disabled.                                                                      |

|      |                                            | 1     | Interrupt request is enabled.                                                                       |

| 0    | AL                                         |       | Arbitration-lost interrupt enable bit                                                               |

|      |                                            | 0     | Interrupt request is disabled.                                                                      |

|      |                                            | 1     | Interrupt request is enabled.                                                                       |

#### 3.3 I2C Interrupt Status Register (ICSTR)

The I2C interrupt status register (ICSTR) is used to determine which interrupt has occurred and to read status information.

The I2C interrupt status register (ICSTR) is shown in Figure 15 and described in Table 7.

Figure 15. I2C Interrupt Status Register (ICSTR)

| 31       |         |         |         |         |         | 16      |         |

|----------|---------|---------|---------|---------|---------|---------|---------|

|          |         |         | Res     | erved   |         |         |         |

|          |         |         | F       | 2-0     |         |         |         |

| 15       | 14      | 13      | 12      | 11      | 10      | 9       | 8       |

| Reserved | SDIR    | NACKSNT | BB      | RSFULL  | XSMT    | AAS     | AD0     |

| R-0      | R/W1C-0 | R/W1C-0 | R/W1C-0 | R-0     | R-1     | R-0     | R-0     |

| 7        | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

| Reserved |         | SCD     | ICXRDY  | ICRRDY  | ARDY    | NACK    | AL      |

| R        | 1-0     | R/W1C-0 | R/W1C-1 | R/W1C-0 | R/W1C-0 | R/W1C-0 | R/W1C-0 |

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear (writing 0 has no effect); -n = value after reset

#### Table 7. I2C Interrupt Status Register (ICSTR) Field Descriptions

| Bit   | Field    | Value | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-15 | Reserved | 0     | These reserved bit locations are always read as zeros. A value written to this field has no effect.                                                                                                                                                                                                                                                                                                    |

| 14    | SDIR     |       | Slave direction bit. In digital-loopback mode (DLB), the SDIR bit is cleared to 0.                                                                                                                                                                                                                                                                                                                     |

|       |          | 0     | I2C is acting as a master-transmitter/receiver or a slave-receiver. SDIR is cleared by one of the following events:                                                                                                                                                                                                                                                                                    |

|       |          |       | A STOP or a START condition.                                                                                                                                                                                                                                                                                                                                                                           |

|       |          |       | SDIR is manually cleared. To clear this bit, write a 1 to it.                                                                                                                                                                                                                                                                                                                                          |

|       |          | 1     | I2C is acting as a slave-transmitter.                                                                                                                                                                                                                                                                                                                                                                  |

| 13    | NACKSNT  |       | No-acknowledgment sent bit. NACKSNT bit is used when the I2C is in the receiver mode. One instance in which NACKSNT is affected is when the NACK mode is used (see the description for NACKMOD in Section 3.9).                                                                                                                                                                                        |

|       |          | 0     | NACK is not sent. NACKSNT is cleared by one of the following events:                                                                                                                                                                                                                                                                                                                                   |

|       |          |       | It is manually cleared. To clear this bit, write a 1 to it.                                                                                                                                                                                                                                                                                                                                            |

|       |          |       | • The I2C is reset (either when 0 is written to the IRS bit of ICMDR or when the processor is reset).                                                                                                                                                                                                                                                                                                  |

|       |          | 1     | NACK is sent. A no-acknowledge bit was sent during the acknowledge cycle on the I2C-bus.                                                                                                                                                                                                                                                                                                               |

| 12    | BB       |       | Bus busy bit. BB bit indicates whether the I2C-bus is busy or is free for another data transfer. In the master mode, BB is controlled by the software.                                                                                                                                                                                                                                                 |

|       |          | 0     | Bus is free. BB is cleared by one of the following events:                                                                                                                                                                                                                                                                                                                                             |

|       |          |       | The I2C receives or transmits a STOP bit (bus free).                                                                                                                                                                                                                                                                                                                                                   |

|       |          |       | BB is manually cleared. To clear this bit, write a 1 to it.                                                                                                                                                                                                                                                                                                                                            |

|       |          |       | • The I2C is reset (either when 0 is written to the IRS bit of ICMDR or when the processor is reset).                                                                                                                                                                                                                                                                                                  |

|       |          | 1     | Bus is busy. When the STT bit in ICMDR is set to 1, a restart condition is generated. BB is set by one of the following events:                                                                                                                                                                                                                                                                        |

|       |          |       | The I2C has received or transmitted a START bit on the bus.                                                                                                                                                                                                                                                                                                                                            |

|       |          |       | SCL is in a low state and the IRS bit in ICMDR is 0.                                                                                                                                                                                                                                                                                                                                                   |

| 11    | RSFULL   |       | Receive shift register full bit. RSFULL indicates an overrun condition during reception. Overrun occurs when the receive shift register (ICRSR) is full with new data but the previous data has not been read from the data receive register (ICDRR). The new data will not be copied to ICDRR until the previous data is read. As new bits arrive from the SDA pin, they overwrite the bits in ICRSR. |

|       |          | 0     | No overrun is detected. RSFULL is cleared by one of the following events:                                                                                                                                                                                                                                                                                                                              |

|       |          |       | ICDRR is read.                                                                                                                                                                                                                                                                                                                                                                                         |

|       |          |       | • The I2C is reset (either when 0 is written to the IRS bit of ICMDR or when the processor is reset).                                                                                                                                                                                                                                                                                                  |

|       |          | 1     | Overrun is detected.                                                                                                                                                                                                                                                                                                                                                                                   |

# Table 7. I2C Interrupt Status Register (ICSTR) Field Descriptions (continued)

| Transmit shift register empty bit. XSMT indicates that the transmitter pass experienced underlifevo cocus when the transmit shift register (ICXSPs) is empty but the data transmit register (ICXDR) and cocus when the transmit shift register (ICXSPs) is empty but the data transmit register (ICXDR) and the same value of the ICDXR-to-ICXSR transfer. The next ICDXR-to-ICXSR transfer. The next ICDXR-to-ICXSR transfer will not occur until new data is in ICDXR. In ew data is not transferred in time, the previous data may be re-transmitted on the SDA pin.  Underflow is detected. XSMT is set by one of the following events:  • Data is written to ICDXR.  • The IC2 is reset (either when 0 is written to the IRS bit of ICMDR or when the processor is reset).  Addressed-as-slave bit.  0 The AAS bit has been cleared by a repeated START condition or by a STOP condition.  1 AAS is set by one of the following events:  • I2C has recognized its own slave address or an address of all zeros (general call).  • The first data word has been received in the free data format (FDF = 1 in ICMDR).  Address ob bit.  0 AD0 has been cleared by a START or STOP condition.  1 An address of all zeros (general call) is detected.  7-6 Reserved  1 These reserved bit locations are always read as zeros. A value written to this field has no effect.  SCD  Stop condition detected bit. SCD indicates when a STOP condition has been detected on the I2C but the STOP condition has been detected. SCD is cleared by one of the following events:  • By reading the INTCODE bits in ICIVR as 110b.  • SCD is manually cleared. To clear this bit, write a 1 to it.  1 A STOP condition has been detected.  1 ICXRDY  Transmit-data-ready interrupt flag bit. ICXRDY indicates that the data transmit register (ICDXR) is read to accept rew data because the previous data has been copied from ICDXR to the transmit shift register (ICXRR). The CPU can poll ICXRDY or use the XRDY interrupt request.  1 ICXRDY is manually cleared. To clear this bit, write a 1 to it.  1 ICXRDY is manually clear | Bit | Field    | Value | Description Descriptions (continued)                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|