User's Guide SLVU5511 – October 2011–Revised September 2014

# Powering the AM335x with the TPS65217x

This User's Guide is a reference for connectivity between the TPS65217 power management IC and the AM335x processor. For detailed information about TPS65217 and AM335x, see the respective data sheets.

## 1 TPS65217 Overview

The TPS65217 is an optimized and highly integrated power management solution for the AM335x processor. Features of the TPS65217 include:

- Power path management for Lithium-ion battery, USB, and AC inputs

- Linear Battery Charger

- 3 DC/DC Step-Down Converters

- 2 LDOs

- 2 Load Switches (configure as LDOs)

- White LED driver capable of driving up to 20 LEDs

There are four versions of the TPS65217:

TPS65217A is used for the AM335x processor in the ZCE package. In this package, the VDD\_MPU and VDD\_CORE nodes are shorted together and will only use a single power rail.

TPS65217B is used for the AM335x processor in the ZCZ package. In this package, the VDD\_MPU and VDD\_CORE rails are separate and can use separate power rails.

TPS65217C is also targeted at the AM335x processor in the ZCZ package, but the DCDC1 output voltage is set to 1.5 V to supply DDR3 memory. This version does not support AM335x RTC-only operation.

TPS65217D is identical to TPS65217C, except DCDC1 is set to 1.35 V to support DDR3L.

| PMIC      | Processor | Memory |

|-----------|-----------|--------|

| TPS65217A | AM335xZCE | DDR2   |

| TPS65217B | AM335xZCZ | DDR2   |

| TPS65217C | AM335xZCZ | DDR3   |

| TPS65217D | AM335xZCZ | DDR3L  |

All trademarks are the property of their respective owners.

Connection Diagram for TPS65217A and AM335x

www.ti.com

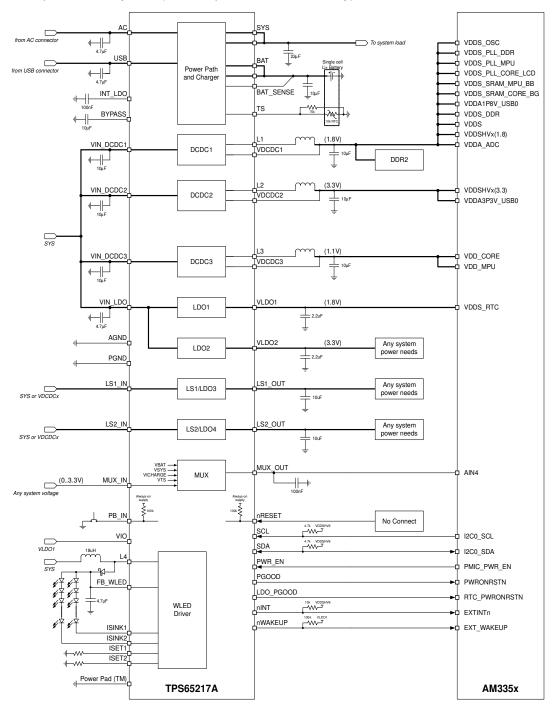

## 2 Connection Diagram for TPS65217A and AM335x

The block diagram shown in Figure 1 illustrates the connections between TPS65217A and AM335x. Power rails as well as the digital and analog signals are shown. The power rails may be used to power additional parts of the system (DCDC1 powers DDR2 memory).

## Power Rails for TPS65217A and AM335x

## 3 Power Rails for TPS65217A and AM335x

Table 1 matches the AM335x power terminals with the appropriate power rail from the TPS65217A.

| TPS65217A | Voltage (V)                                        | AM335x            |

|-----------|----------------------------------------------------|-------------------|

|           |                                                    | VDDS_DDR          |

|           |                                                    | VDDS              |

|           |                                                    | VDDSHVx(1.8 V)    |

|           |                                                    | VDDS_SRAM_CORE_BG |

|           |                                                    | VDDS_SRAM_MPU_BB  |

| DCDC1     | 1.8                                                | VDD_PLL_DDR       |

|           |                                                    | VDDS_PLL_CORE_LCD |

|           |                                                    | VDDS_PLL_MPU      |

|           |                                                    | VDDS_OSC          |

|           |                                                    | VDDA1P8V_USB0/1   |

|           |                                                    | VDDA_ADC          |

| DCDC2     | 3.3                                                | VDDSHVx(3.3 V)    |

| DCDC2     | 3.5                                                | VDDA3P3V_USB0/1   |

| DCDC3     | Defaults to 1.1.1/ Controlled by 12C               | VDD_CORE          |

| DCDC3     | Defaults to 1.1 V. Controlled by I <sup>2</sup> C. | VDD_MPU           |

| LDO1      | 1.8                                                | VDDS_RTC          |

| LDO2      | 3.3                                                | n/a               |

| LDO3/LS1  | Load Switch                                        | n/a               |

| LDO4/LS2  | Load Switch                                        | n/a               |

## Table 1. Power Rails for TPS65217A and AM335x

Each output voltage may be changed dynamically while the TPS65217 is in active mode. This requires use of I<sup>2</sup>C commands to the TPS65217.

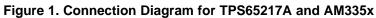

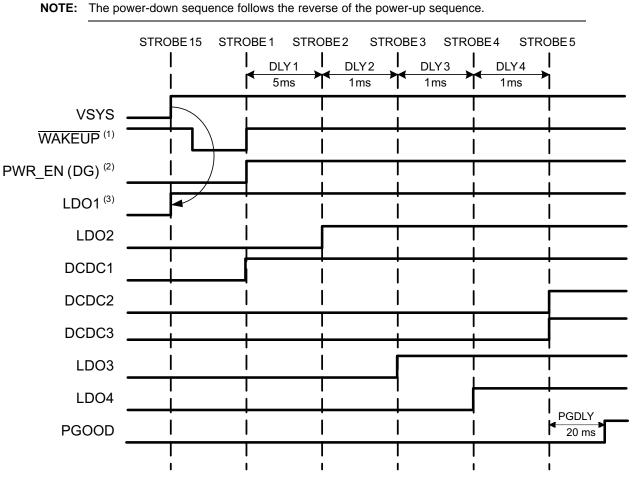

## 4 Power-Up Sequence for TPS65217A

Figure 2 and Table 2 describe the power-up sequence of the TPS65217A. This sequence is optimized specifically for the AM335x processor.

(1) Wakeup $\downarrow$  events are PB\_IN $\downarrow$  or AC $\uparrow$  or USB $\uparrow$

(2) DG = Deglitched

(3) LDO1 turns on as soon as VSYS is present

LDO\_PGOOD $\uparrow$  20 ms after LDO1 $\uparrow$

## Figure 2. Power-Up Sequence Timing Diagram, TPS65217A

| ·····     |       |  |  |

|-----------|-------|--|--|

| STROBE 15 | LDO1  |  |  |

| STROBE 1  | DCDC1 |  |  |

|           | LS1   |  |  |

| STROBE 2  | DCDC2 |  |  |

|           | LDO2  |  |  |

| STROBE 3  | DCDC3 |  |  |

| STROBE 4  | LS2   |  |  |

# Table 2. TPS65217A, Power-Up Sequence

Connections Diagram for TPS65217B and AM335x

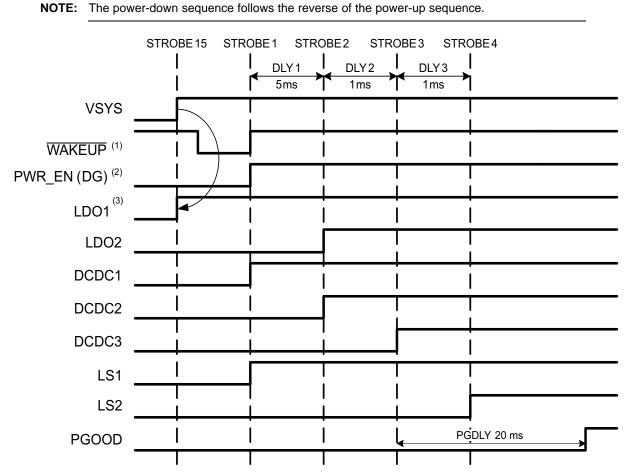

## 5 Connections Diagram for TPS65217B and AM335x

The block diagram shown in Figure 3 illustrates the connections between TPS65217B and AM335x. Power rails as well as the digital and analog signals are shown. The power rails may be used to power additional parts of the system (DCDC1 powers DDR2 memory).

Figure 3. Connection Diagram for TPS65217B and AM335x

## 6 Power Rails Connections for TPS65217B and AM335x

Table 3 matches the AM335x power terminals with the appropriate power rail from the TPS65217B.

| TPS65217B | Voltage (V)                                        | AM335x            |

|-----------|----------------------------------------------------|-------------------|

|           |                                                    | VDDS_DDR          |

|           |                                                    | VDDS              |

|           |                                                    | VDDSHVx(1.8 V)    |

|           |                                                    | VDDS_SRAM_CORE_BG |

|           |                                                    | VDDS_SRAM_MPU_BB  |

| DCDC1     | 1.8                                                | VDD_PLL_DDR       |

|           |                                                    | VDDS_PLL_CORE_LCD |

|           |                                                    | VDDS_PLL_MPU      |

|           |                                                    | VDDS_OSC          |

|           |                                                    | VDDA1P8V_USB0/1   |

|           |                                                    | VDDA_ADC          |

| DCDC2     | Defaults to 1.1 V. Controlled by I <sup>2</sup> C. | VDD_MPU           |

| DCDC3     | Defaults to 1.1 V. Controlled by I <sup>2</sup> C. | VDD_CORE          |

| LDO1      | 1.8                                                | VDDS_RTC          |

| LDO2      | 3.3                                                | n/a               |

| LDO3/LS1  | 3 2 (1 DO)                                         | VDDSHVx(3.3 V)    |

| LDO3/L81  | 3.3 (LDO)                                          | VDDA3P3V_USB0/1   |

| LDO4/LS2  | 3.3 (LDO)                                          | VDDSHVx(3.3 V)    |

## Table 3. Power Rails for TPS65217B and AM335x

Each output voltage may be changed dynamically while the TPS65217 is in active mode. This requires use of I<sup>2</sup>C commands to the TPS65217.

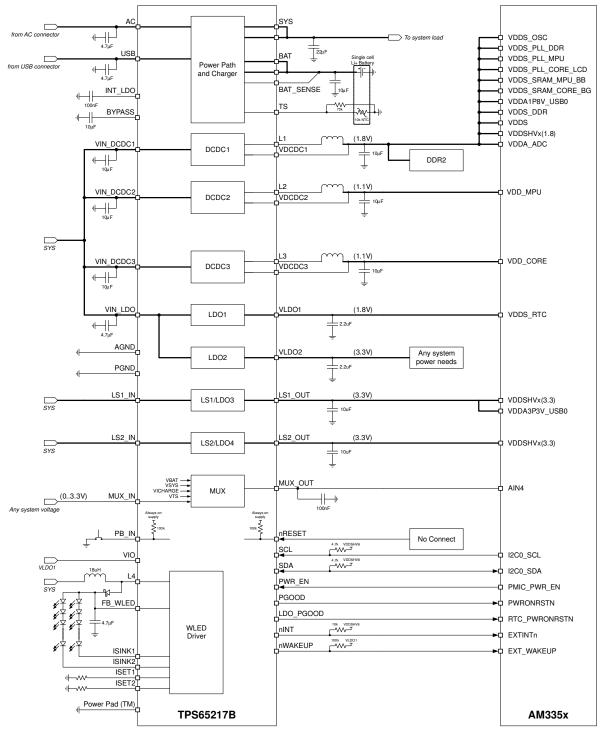

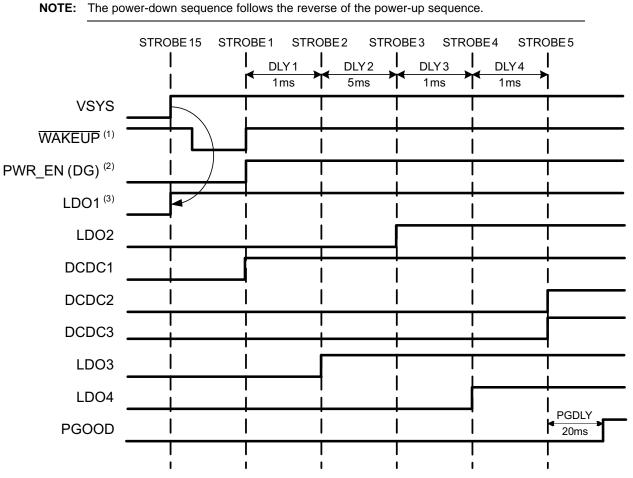

### 7 Power-Up Sequence for TPS65217B

Figure 4 and Table 4 describe the power-up sequence of the TPS65217B. This sequence is optimized specifically for the AM335x processor.

(1) Wakeup $\downarrow$  events are PB\_IN $\downarrow$  or AC $\uparrow$  or USB $\uparrow$

(2) DG = Deglitched

(3) LDO1 turns on as soon as VSYS is present

LDO\_PGOOD↑ 20 ms after LDO1↑

## Figure 4. Power-Up Sequence Timing Diagram, TPS65217B

| STROBE 15 | LDO1  |  |

|-----------|-------|--|

| STROBE 1  | DCDC1 |  |

| STROBE 2  | LDO2  |  |

| STROBE 3  | LDO3  |  |

| STROBE 4  | LDO4  |  |

| STROBE 5  | DCDC2 |  |

| STROBE 5  | DCDC3 |  |

#### Table 4. TPS65217B Power-Up Sequence

Connections Diagram for TPS65217C and AM335x

www.ti.com

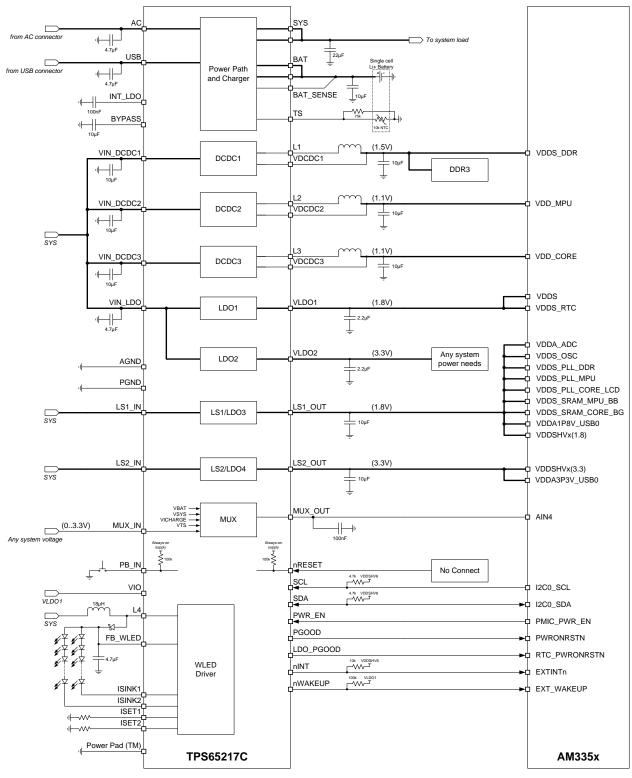

## 8 Connections Diagram for TPS65217C and AM335x

The block diagram shown in Figure 5 illustrates the connections between TPS65217C and AM335x. Power rails as well as the digital and analog signals are shown. The power rails may be used to power additional parts of the system (DCDC1 powers DDR3 memory).

## 9 Power Rails Connections for TPS65217C and AM335x

Table 5 matches the AM335x power terminals with the appropriate power rail from the TPS65217C.

| TPS65217C | Voltage (V)                                        | AM335x            |

|-----------|----------------------------------------------------|-------------------|

| DCDC1     | 1.5                                                | VDDS_DDR          |

| DCDC2     | Defaults to 1.1 V. Controlled by I <sup>2</sup> C. | VDD_MPU           |

| DCDC3     | Defaults to 1.1 V. Controlled by I <sup>2</sup> C. | VDD_CORE          |

| LDO1      | 1.8                                                | VDDS_RTC          |

|           |                                                    | VDDS              |

| LDO2      | 3.3                                                | n/a               |

| LDO3/LS1  | 1.8                                                | VDDSHVx(1.8 V)    |

|           |                                                    | VDDS_SRAM_CORE_BG |

|           |                                                    | VDDS_SRAM_MPU_BB  |

|           |                                                    | VDDS_PLL_DDR      |

|           |                                                    | VDDS_PLL_CORE_LCD |

|           |                                                    | VDDS_OSC          |

|           |                                                    | VDDA1P8V_USB0/1   |

|           |                                                    | VDDA_ADC          |

| LDO4/LS2  | 3.3                                                | VDDSHVx(3.3 V)    |

|           |                                                    | VDDA3P3V_USV0/1   |

## Table 5. Power Rails for TPS65217C and AM335x

Each output voltage may be changed dynamically while the TPS65217 is in active mode. This requires use of  $I^2C$  commands to the TPS65217.

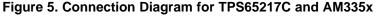

## **10 Power-Up Sequence for TPS65217C**

Figure 6 and Table 6 describe the power-up sequence of the TPS65217C. This sequence is optimized specifically for the AM335x processor.

(1) Wakeup $\downarrow$  events are PB\_IN $\downarrow$  or AC $\uparrow$  or USB $\uparrow$

(2) DG = Deglitched

(3) LDO1 turns on as soon as VSYS is present

LDO\_PGOOD↑ 20 ms after LDO1↑

## Figure 6. Power-Up Sequence Timing Diagram, TPS65217C

| STROBE 15 | LDO1  |

|-----------|-------|

| STROBE 1  | DCDC1 |

| STROBE 2  | LDO3  |

| STROBE 3  | LDO2  |

| STROBE 4  | LDO4  |

| STROBE 5  | DCDC2 |

| STROBE 5  | DCDC3 |

### Table 6. TPS65217C Power-Up Sequence

## 11 **PGOOD and LDO\_PGOOD Outputs**

PGOOD and LDO\_PGOOD are push-pull outputs. These outputs are supplied by the VIO pin. During TPS65217 SLEEP mode, all power rails are typically turned off except for LDO1. In order for LDO\_PGOOD to remain high during SLEEP mode, connect the VIO pin to LDO1. This allows the LDO\_PGOOD signal to be valid even during SLEEP mode. With VIO connected to LDO1, PGOOD and LDO\_PGOOD have an output high level of 1.8 V. This level meets the requirements of the PWRONRSTN and RTC\_PWRONRSTN input signals of the AM335x processor.

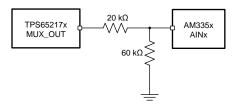

## 12 MUX\_OUT Scaling

The AINx ADC input of the AM335x processor is powered by VDDA\_ADC. Therefore the maximum voltage input to the ADC should be 1.8 V. If the output voltage of MUX\_OUT will be higher than 1.8 V in your application, then add a resistor divider inbetween MUX\_OUT and AINx, such that the voltage at AINx does not exceed 1.8 V. The resistor values must be large enough such that the load on MUX\_OUT is low. However, the resistors should not be so large as to impact the performance of the ADC.

Figure 7. MUX\_OUT Scaling Example

## 13 Pull-Up Resistors

There are four pull-up resistors on the connection diagrams; Figure 1, Figure 3, and Figure 5. nWAKEUP should be pulled up to VLDO1 so that the pull-up source is present even during SLEEP mode. A 100-k $\Omega$  pull-up resistor should be used for nWAKEUP to minimize the current load on LDO1. nINT, SCL, and SDA should be pulled up to the same supply that is connected to VDDSHV6. If VDDSHV6 is 1.8 V, then the 1.8-V supply should be used. If VDDSHV6 is 3.3 V, then the 3.3-V supply should be used. SCL and SDA use lower value pull-up resistors in order to decrease rise time of these nodes during I<sup>2</sup>C communication.

## **Revision History**

| Changes from G Revision (March 2013) to H Revision |                                                                |   |

|----------------------------------------------------|----------------------------------------------------------------|---|

| •                                                  | Changed connection diagram for TPS65217C and AM335x.           | 8 |

| •                                                  | Changed table contents in Power Rails for TPS65217C and AM335x | 9 |

## **Revision History**

| C | hanges from H Revision (January 2014) to I Revision  | Page |

|---|------------------------------------------------------|------|

| • | Changed connection diagram for TPS65217C and AM335x. | 8    |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ctivity                       |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2014, Texas Instruments Incorporated