# **TMS320C28x Extended Instruction Sets**

# **Technical Reference Manual**

Literature Number: SPRUHS1C

October 2014–Revised November 2019

# **Contents**

| Pref | face |                                                                | 9          |

|------|------|----------------------------------------------------------------|------------|

| 1    | Floa | ting Point Unit (FPU)                                          | 11         |

|      | 1.1  | Overview                                                       |            |

|      |      | 1.1.1 Compatibility with the C28x Fixed-Point CPU              |            |

|      | 1.2  | Components of the C28x plus Floating-Point CPU                 |            |

|      |      | 1.2.1 Emulation Logic                                          |            |

|      |      | 1.2.2 Memory Map                                               |            |

|      |      | 1.2.3 On-Chip Program and Data                                 |            |

|      |      | 1.2.4 CPU Interrupt Vectors                                    |            |

|      |      | 1.2.5 Memory Interface                                         |            |

|      | 1.3  | CPU Register Set                                               |            |

|      |      | 1.3.1 CPU Registers                                            |            |

|      | 1.4  | Pipeline                                                       |            |

|      |      | 1.4.1 Pipeline Overview                                        |            |

|      |      | 1.4.2 General Guidelines for Floating-Point Pipeline Alignment |            |

|      |      | 1.4.3 Moves from FPU Registers to C28x Registers               |            |

|      |      | 1.4.4 Moves from C28x Registers to FPU Registers               |            |

|      |      | 1.4.5 Parallel Instructions                                    |            |

|      |      | 1.4.6 Invalid Delay Instructions                               |            |

|      |      | 1.4.7 Optimizing the Pipeline                                  |            |

|      | 1.5  | Floating Point Unit Instruction Set                            |            |

|      |      | 1.5.1 Instruction Descriptions                                 |            |

|      |      | 1.5.2 Instructions                                             |            |

| 2    | Floa | ting Point Unit (FPU64)                                        |            |

| _    | 2.1  | Overview                                                       |            |

|      | 2.1  | 2.1.1 Compatibility with the C28x Fixed-Point CPU              |            |

|      | 2.2  | Components of the C28x plus Floating-Point CPU (FPU64)         |            |

|      | 2.2  | 2.2.1 Emulation Logic                                          |            |

|      |      | 2.2.2 Memory Map                                               |            |

|      |      | 2.2.3 On-Chip Program and Data                                 |            |

|      |      | 2.2.4 CPU Interrupt Vectors                                    |            |

|      |      | 2.2.5 Memory Interface                                         |            |

|      | 2.3  | CPU Register Set                                               |            |

|      | 2.0  | 2.3.1 CPU Registers                                            |            |

|      | 2.4  | Pipeline                                                       |            |

|      | ۷.٦  | 2.4.1 Pipeline Overview                                        |            |

|      |      | 2.4.2 General Guidelines for Floating-Point Pipeline Alignment |            |

|      |      | 2.4.3 Moves from FPU Registers to C28x Registers               |            |

|      |      | 2.4.4 Moves from C28x Registers to FPU Registers               |            |

|      |      |                                                                | 157<br>157 |

|      |      |                                                                | 157<br>158 |

|      |      | •                                                              | 161        |

|      | 2.5  |                                                                | 161<br>162 |

|      | ۷.ن  |                                                                | 162<br>162 |

|      |      | •                                                              | 162<br>165 |

|      |      | Z.U.Z IIIUUUUUII0                                              | , UU       |

#### www.ti.com

| 3 | Viter<br>3.1 |         | mplex Math and CRC Unit (VCU)                            |     |

|---|--------------|---------|----------------------------------------------------------|-----|

|   | 3.1          |         | onents of the C28x plus VCU                              |     |

|   | -            | •       | •                                                        |     |

|   | 3.3          |         | ation Logic                                              |     |

|   |              | 3.3.1   | Memory Map                                               |     |

|   |              | 3.3.2   | CPU Interrupt Vectors                                    |     |

|   |              | 3.3.3   | Memory Interface                                         |     |

|   |              | 3.3.4   | Address and Data Buses                                   |     |

|   | 0.4          | 3.3.5   | Alignment of 32-Bit Accesses to Even Addresses           |     |

|   | 3.4          | -       | ter Set                                                  |     |

|   |              | 3.4.1   | VCU Register Set                                         |     |

|   |              | 3.4.2   | VCU Status Register (VSTATUS)                            |     |

|   |              | 3.4.3   | Repeat Block Register (RB)                               |     |

|   | 3.5          | •       | ne                                                       |     |

|   |              | 3.5.1   | Pipeline Overview                                        |     |

|   |              | 3.5.2   | General Guidelines for Floating-Point Pipeline Alignment |     |

|   |              | 3.5.3   | Parallel Instructions                                    |     |

|   |              | 3.5.4   | Invalid Delay Instructions                               |     |

|   | 3.6          | Instru  | ction Set                                                |     |

|   |              | 3.6.1   | Instruction Descriptions                                 |     |

|   |              | 3.6.2   | General Instructions                                     |     |

|   |              | 3.6.3   | Complex Math Instructions                                | 389 |

|   |              | 3.6.4   | Cyclic Redundancy Check (CRC) Instructions               |     |

|   |              | 3.6.5   | Viterbi Instructions                                     | 439 |

|   | 3.7          | Round   | ding Mode                                                | 461 |

| 4 | Cycl         | ic Redu | undancy Check (VCRC)                                     | 463 |

|   | 4.1          |         | iew                                                      |     |

|   | 4.2          |         | Code Development                                         |     |

|   | 4.3          |         | onents of the C28x Plus VCRC                             |     |

|   |              | 4.3.1   | Emulation Logic                                          |     |

|   |              | 4.3.2   | Memory Map                                               |     |

|   |              | 4.3.3   | CPU Interrupt Vectors                                    |     |

|   |              | 4.3.4   | Memory Interface                                         |     |

|   |              | 4.3.5   | Address and Data Buses                                   |     |

|   |              | 4.3.6   | Alignment of 32-Bit Accesses to Even Addresses           |     |

|   | 4.4          |         | ter Set                                                  |     |

|   |              |         | VCRC Register Set                                        |     |

|   | 4.5          | Pipelir |                                                          |     |

|   | 1.0          | 4.5.1   | Pipeline Overview                                        |     |

|   |              | 4.5.2   | General Guidelines for VCRC Pipeline Alignment           |     |

|   | 4.6          |         | ction Set                                                |     |

|   | 4.0          | 4.6.1   | Instruction Descriptions                                 |     |

|   |              | 4.6.2   | General Instructions                                     |     |

| _ |              | _       |                                                          |     |

| 5 | C28          |         | , Complex Math and CRC Unit-II (VCU-II)                  |     |

|   | 5.1          |         | iew                                                      |     |

|   | 5.2          | Comp    | onents of the C28x Plus VCU                              |     |

|   |              | 5.2.1   | Emulation Logic                                          |     |

|   |              | 5.2.2   | Memory Map                                               |     |

|   |              | 5.2.3   | CPU Interrupt Vectors                                    | 511 |

|   |              | 5.2.4   | Memory Interface                                         | 511 |

|   |              | 5.2.5   | Address and Data Buses                                   | 511 |

|   |              | 5.2.6   | Alignment of 32-Bit Accesses to Even Addresses           | 512 |

|   | 5.3          | Regist  | ter Set                                                  | 513 |

|   |              |         |                                                          |     |

|   |       | 5.3.1   | VCU Register Set                                                        | 514        |

|---|-------|---------|-------------------------------------------------------------------------|------------|

|   |       | 5.3.2   | VCU Status Register (VSTATUS)                                           |            |

|   |       | 5.3.3   | Repeat Block Register (RB)                                              |            |

|   | 5.4   |         |                                                                         |            |

|   | 5.4   | •       | Ne                                                                      | _          |

|   |       | 5.4.1   | Pipeline Overview                                                       | 521        |

|   |       | 5.4.2   | General Guidelines for VCU Pipeline Alignment                           |            |

|   |       | 5.4.3   | Parallel Instructions                                                   |            |

|   |       | 5.4.4   | Invalid Delay Instructions                                              | 523        |

|   | 5.5   | Instruc | ction Set                                                               | 526        |

|   |       | 5.5.1   | Instruction Descriptions                                                | 526        |

|   |       | 5.5.2   | General Instructions                                                    | 528        |

|   |       | 5.5.3   | Arithmetic Math Instructions                                            | 572        |

|   |       | 5.5.4   | Complex Math Instructions                                               | 579        |

|   |       | 5.5.5   | Cyclic Redundancy Check (CRC) Instructions                              |            |

|   |       | 5.5.6   | Deinterleaver Instructions.                                             |            |

|   |       | 5.5.7   | FFT Instructions.                                                       |            |

|   |       | 5.5.8   | Galois Instructions                                                     |            |

|   |       | 5.5.9   | Viterbi Instructions                                                    |            |

|   | F 0   |         |                                                                         |            |

|   | 5.6   |         | ling Mode                                                               |            |

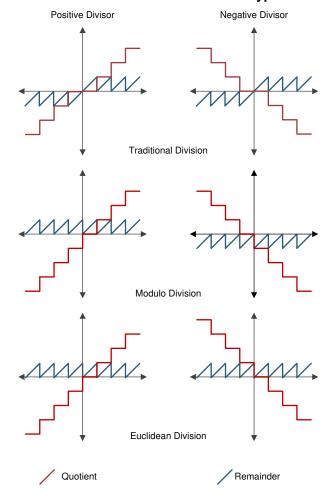

| 6 | Fast  | Integer | Division Unit (FINTDIV)                                                 | <b>748</b> |

|   | 6.1   | Overvi  | ew                                                                      | 749        |

|   |       | 6.1.1   | Compatibility With the C28x Fixed-Point CPU and C28x Floating Point CPU | 749        |

|   |       | 6.1.2   | Fast Integer Division Code development                                  | 749        |

|   | 6.2   | Compo   | onents of the C28x plus FINTDIV (C28x+FINTDIV)                          | <b>750</b> |

|   | 6.3   | CPU F   | Register Set                                                            | 750        |

|   | 6.4   | Pipelin | 1e                                                                      | 750        |

|   | 6.5   |         | of Divisions supported by C28x+FINTDIV                                  |            |

|   | 6.6   |         | Fast Integer Division – Fast Integer Division Instruction Set           |            |

|   |       | 6.6.1   | Instruction Descriptions                                                |            |

|   |       | 6.6.2   | Instructions                                                            |            |

| 7 | Triac | nomot   | ric Math Unit (TMU)                                                     |            |

| 7 | _     |         | ` ,                                                                     |            |

|   | 7.1   |         | ew                                                                      |            |

|   | 7.2   | •       | onents of the C28x+FPU Plus TMU                                         |            |

|   |       | 7.2.1   | Interrupt Context Save and Restore                                      |            |

|   | 7.3   |         | Format                                                                  | 774        |

|   |       | 7.3.1   | Floating Point Encoding                                                 | 774        |

|   |       | 7.3.2   | Negative Zero:                                                          | 774        |

|   |       | 7.3.3   | De-Normalized Numbers:                                                  | 774        |

|   |       | 7.3.4   | Underflow:                                                              | 774        |

|   |       | 7.3.5   | Overflow:                                                               | 774        |

|   |       | 7.3.6   | Rounding:                                                               | 774        |

|   |       | 7.3.7   | Infinity and Not a Number (NaN):                                        | 774        |

|   | 7.4   |         | ne                                                                      | 775        |

|   |       | 7.4.1   | Pipeline and Register Conflicts                                         | 775        |

|   |       | 7.4.2   | Delay Slot Requirements                                                 | 777        |

|   |       | 7.4.3   | Effect of Delay Slot Operations on the Flags                            | 778        |

|   |       | 7.4.4   | Multi-Cycle Operations in Delay Slots                                   | 778        |

|   |       | 7.4.4   | Moves From FPU Registers to C28x Registers                              | 779        |

|   | 7 5   |         |                                                                         |            |

|   | 7.5   |         | nstruction Set                                                          | 780        |

|   |       | 7.5.1   | Instruction Descriptions                                                | 780        |

|   |       | 7.5.2   | Common Restrictions                                                     | 782        |

|   |       | 7.5.3   | TMU Type 0 Instructions                                                 | 782        |

|   |       | 7.5.4   | TMU Type 1 Instructions                                                 | 796        |

| www. | ti | CO | m |

|------|----|----|---|

# **List of Figures**

| 1-1. | FPU Functional Block Diagram                                                      | . 12 |

|------|-----------------------------------------------------------------------------------|------|

| 1-2. | C28x With Floating-Point Registers                                                | . 16 |

| 1-3. | Floating-point Unit Status Register (STF)                                         | . 18 |

| 1-4. | Repeat Block Register (RB)                                                        | . 20 |

| 1-5. | FPU Pipeline                                                                      |      |

| 2-1. | FPU64 Functional Block Diagram                                                    | 145  |

| 2-2. | C28x With FPU64 Floating-Point Registers                                          | 148  |

| 2-3. | Floating-point Unit Status Register (STF)                                         | 151  |

| 2-4. | Repeat Block Register (RB)                                                        |      |

| 2-5. | FPU64 Pipeline                                                                    | 154  |

| 3-1. | C28x + VCU Block Diagram                                                          | 340  |

| 3-2. | C28x + FPU + VCU Registers                                                        | 344  |

| 3-3. | VCU Status Register (VSTATUS)                                                     | 346  |

| 3-4. | Repeat Block Register (RB)                                                        |      |

| 3-5. | C28x + FCU + VCU Pipeline                                                         | 351  |

| 4-1. | C28x + VCRC Block Diagram                                                         | 464  |

| 4-2. | C28x + VCRC Registers                                                             | 467  |

| 5-1. | C28x + VCU Block Diagram                                                          | 509  |

| 5-2. | C28x + FPU + VCU Registers                                                        | 513  |

| 5-3. | VCU Status Register (VSTATUS)                                                     | 516  |

| 5-4. | Repeat Block Register (RB)                                                        | 519  |

| 5-5. | C28x + FCU + VCU Pipeline                                                         | 521  |

| 6-1. | Transfer Function for Different Types of Division                                 | 751  |

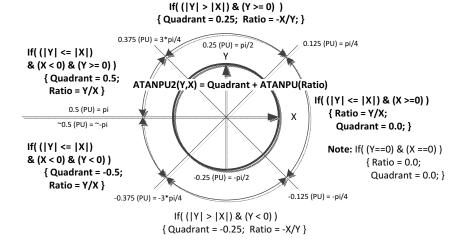

| 7-1. | Calculation of RaH (Quadrant) and RbH (Ratio) Based on RcH (Y) and RdH (X) Values | 793  |

|      |                                                                                   |      |

### **List of Tables**

| 1-1.  | 28x Plus Floating-Point CPU Register Summary                                     | . 17 |

|-------|----------------------------------------------------------------------------------|------|

| 1-2.  | Floating-point Unit Status (STF) Register Field Descriptions                     | . 18 |

| 1-3.  | Repeat Block (RB) Register Field Descriptions                                    | . 20 |

| 1-4.  | Operand Nomenclature                                                             | . 30 |

| 1-5.  | Summary of Instructions                                                          | . 32 |

| 2-1.  | 28x Plus Floating-Point FPU64 CPU Register Summary                               | 149  |

| 2-2.  | Floating-point Unit Status (STF) Register Field Descriptions                     | 151  |

| 2-3.  | Repeat Block (RB) Register Field Descriptions                                    | 153  |

| 2-4.  | Operand Nomenclature                                                             | 163  |

| 2-5.  | Summary of Instructions                                                          | 165  |

| 3-1.  | Viterbi Decode Performance                                                       | 339  |

| 3-2.  | Complex Math Performance                                                         | 339  |

| 3-3.  | VCU Register Set                                                                 | 345  |

| 3-4.  | 28x CPU Register Summary                                                         | 346  |

| 3-5.  | VCU Status (VSTATUS) Register Field Descriptions                                 | 347  |

| 3-6.  | Operation Interaction with VSTATUS Bits                                          | 347  |

| 3-7.  | Repeat Block (RB) Register Field Descriptions                                    | 349  |

| 3-8.  | Operand Nomenclature                                                             | 356  |

| 3-9.  | INSTRUCTION dest, source1, source2 Short Description                             | 357  |

| 3-10. | General Instructions                                                             | 358  |

| 3-11. | Complex Math Instructions                                                        | 389  |

| 3-12. | CRC Instructions                                                                 | 427  |

| 3-13. | Viterbi Instructions                                                             | 439  |

| 3-14. | Example: Values Before Shift Right                                               | 461  |

| 3-15. | Example: Values after Shift Right                                                | 461  |

| 3-16. | Example: Addition with Right Shift and Rounding                                  | 461  |

| 3-17. | Example: Addition with Rounding After Shift Right                                | 461  |

| 3-18. | Shift Right Operation With and Without Rounding                                  | 461  |

| 4-1.  | VCRC Status (VSTATUS) Register Field Descriptions                                |      |

| 4-2.  | VCRC: The CRC result register for unsecured memories                             |      |

| 4-3.  | VCRCPOLY: The CRC Polynomial register for generic CRC instructions               |      |

| 4-4.  | VCRCSIZE: The CRC Polynomial and Data Size register for generic CRC instructions |      |

| 4-5.  | VCUREV: VCU revision register                                                    | 468  |

| 4-6.  | Operand Nomenclature                                                             | 471  |

| 4-7.  | INSTRUCTION dest, source1, source2 Short Description                             |      |

| 4-8.  | General Instructions                                                             |      |

| 5-1.  | Viterbi Decode Performance                                                       |      |

| 5-2.  | Complex Math Performance                                                         |      |

| 5-3.  | VCU Register Set                                                                 |      |

| 5-4.  | 28x CPU Register Summary                                                         |      |

| 5-5.  | VCU Status (VSTATUS) Register Field Descriptions                                 |      |

| 5-6.  | Operation Interaction With VSTATUS Bits                                          |      |

| 5-7.  | Repeat Block (RB) Register Field Descriptions                                    |      |

| 5-8.  | Operations Requiring a Delay Slot(s)                                             |      |

| 5-9.  | Operand Nomenclature                                                             |      |

| 5-10. | INSTRUCTION dest, source1, source2 Short Description                             |      |

| 5-11. | General Instructions                                                             | 528  |

#### www.ti.com

| 5-12. | Arithmetic Math Instructions                       | 572         |

|-------|----------------------------------------------------|-------------|

| 5-13. | Complex Math Instructions                          | <b>57</b> 9 |

| 5-14. | CRC Instructions                                   | 638         |

| 5-15. | Deinterleaver Instructions                         | 654         |

| 5-16. | FFT Instructions                                   | 670         |

| 5-17. | Galois Field Instructions                          | 698         |

| 5-18. | Viterbi Instructions                               | 711         |

| 5-19. | Example: Values Before Shift Right                 | 746         |

| 5-20. | Example: Values after Shift Right                  | 746         |

| 5-21. | Example: Addition with Right Shift and Rounding    | 746         |

| 5-22. | Example: Addition with Rounding After Shift Right  | 746         |

| 5-23. | Shift Right Operation With and Without Rounding    | 747         |

| 6-1.  | Operand Nomenclature                               | 752         |

| 6-2.  | Summary of Instructions                            | 754         |

| 7-1.  | TMU Type 0 Instructions                            | 773         |

| 7-2.  | TMU Type 1 Additional Instructions                 | 773         |

| 7-3.  | IEEE 32-Bit Single Precision Floating-Point Format | 774         |

| 7-4.  | Delay Slot Requirements for TMU Instructions       | 777         |

| 7-5.  | Operand Nomenclature                               | 780         |

| 7-6.  | Summary of Instructions                            | 782         |

| 7-7.  | Summary of Instructions                            | 796         |

# Read This First

This document describes the architecture, pipeline, and instruction sets of the TMU, VCRC, VCU-II, FPU32, and FPU64 accelerators.

#### **About This Manual**

The TMS320C2000™ digital signal processor (DSP) platform is part of the TMS320™ DSP family.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h or with a leading 0x. For example, the following number is 40 hexadecimal (decimal 64): 40h or 0x40.

- Registers in this document are shown as figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### Related Documentation

The following books describe the TMS320x28x and related support tools that are available on the TI website:

#### Data Manual and Errata—

- **SPRS439** TMS320F2833x, TMS320F2823x Digital Signal Controllers (DSCs) Data Manual contains the pinout, signal descriptions, as well as electrical and timing specifications.

- **SPRZ272** TMS320F2833x, TMS320F2823x DSC Silicon Errata describes known advisories on silicon and provides workarounds.

- **SPRS516** TMS320C2834x Delfino Microcontrollers Data Manual contains the pinout, signal descriptions, as well as electrical and timing specifications.

- **SPRZ267** TMS320C2834x Delfino™ MCUs Silicon Errata describes known advisories on silicon and provides workarounds.

- **SPRS698** TMS320F2806x Piccolo™ Microcontrollers Data Manual contains the pinout, signal descriptions, as well as electrical and timing specifications.

- SPRZ342— TMS320F2806x Piccolo™ MCUs Silicon Errata describes known advisories on silicon and provides workarounds.

- SPRS742— F28M35x Concerto™ Microcontrollers Data Manual contains the pinout, signal descriptions, as well as electrical and timing specifications.

- SPRZ357— F28M35x Concerto™ MCUs Silicon Errata describes known advisories on silicon and provides workarounds.

- **SPRS825** F28M36x Concerto™ Microcontrollers Data Manual contains the pinout, signal descriptions, as well as electrical and timing specifications.

- **SPRZ375** F28M36x Concerto™ MCUs Silicon Errata describes known advisories on silicon and provides workarounds.

Related Documentation www.ti.com

- **SPRS880** TMS320F2837xD Dual-Core Delfino™ Microcontrollers Data Manual contains the pinout, signal descriptions, as well as electrical and timing specifications.

- **SPRZ412** TMS320F2837xD Dual-Core Delfino™ MCUs Silicon Errata describes known advisories on silicon and provides workarounds.

- **SPRS881** TMS320F2837xS Delfino™ Microcontrollers Data Manual contains the pinout, signal descriptions, as well as electrical and timing specifications.

- **SPRZ422** TMS320F2837xS Delfino™ MCUs Silicon Errata describes known advisories on silicon and provides workarounds.

- SPRS902— TMS320F2807x Piccolo™ Microcontrollers Data Manual contains the pinout, signal descriptions, as well as electrical and timing specifications.

- **SPRZ423** TMS320F2807x Piccolo™ MCUs Silicon Errata describes known advisories on silicon and provides workarounds.

- **SPRS945** TMS320F28004x Piccolo™ Microcontrollers Data Manual contains the pinout, signal descriptions, as well as electrical and timing specifications.

- **SPRZ439** TMS320F28004x Piccolo™ Microcontrollers Silicon Errata describes known advisories on silicon and provides workarounds.

- **SPRSP14** TMS320F2838x Microcontrollers With Connectivity Manager Data Manual contains the pinout, signal descriptions, as well as electrical and timing specifications.

- SPRZ458— TMS320F2838x MCUs Silicon Errata describes known advisories on silicon and provides workarounds.

#### **Trademarks**

Delfino, Piccolo, Concerto, TMS320C2000 are trademarks of Texas Instruments.

# Floating Point Unit (FPU)

The TMS320C2000<sup>™</sup> DSP family consists of fixed-point and floating-point digital signal controllers (DSCs). TMS320C2000<sup>™</sup> Digital Signal Controllers combine control peripheral integration and ease of use of a microcontroller (MCU) with the processing power and C efficiency of Tl's leading DSP technology. This chapter provides an overview of the architectural structure and components of the C28x plus floating-point unit CPU.

Topic Page

| 1.1 | Overview                                       | 12 |

|-----|------------------------------------------------|----|

| 1.2 | Components of the C28x plus Floating-Point CPU | 13 |

| 1.3 | CPU Register Set                               | 15 |

| 1.4 | Pipeline                                       | 21 |

| 1.5 | Floating Point Unit Instruction Set            | 29 |

Overview www.ti.com

#### 1.1 Overview

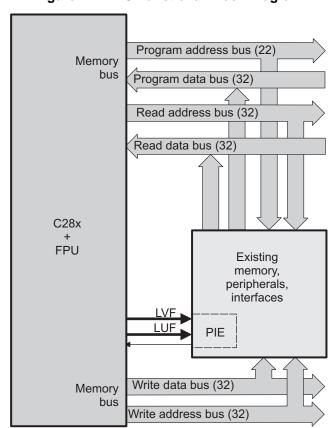

The C28x plus floating-point (C28x+FPU) processor extends the capabilities of the C28x fixed-point CPU by adding registers and instructions to support IEEE single-precision floating point operations. This device draws from the best features of digital signal processing; reduced instruction set computing (RISC); and microcontroller architectures, firmware, and tool sets. The DSC features include a modified Harvard architecture and circular addressing. The RISC features are single-cycle instruction execution, register-to-register operations, and modified Harvard architecture (usable in Von Neumann mode). The microcontroller features include ease of use through an intuitive instruction set, byte packing and unpacking, and bit manipulation. The modified Harvard architecture of the CPU enables instruction and data fetches to be performed in parallel. The CPU can read instructions and data while it writes data simultaneously to maintain the single-cycle instruction operation across the pipeline. The CPU does this over six separate address/data buses.

Throughout this document the following notations are used:

- C28x refers to the C28x fixed-point CPU.

- C28x plus Floating-Point and C28x+FPU both refer to the C28x CPU with enhancements to support IEEE single-precision floating-point operations.

#### 1.1.1 Compatibility with the C28x Fixed-Point CPU

No changes have been made to the C28x base set of instructions, pipeline, or memory bus architecture. Therefore, programs written for the C28x CPU are completely compatible with the C28x+FPU and all of the features of the C28x documented in *TMS320C28x DSP CPU and Instruction Set Reference Guide* (literature number SPRU430) apply to the C28x+FPU.

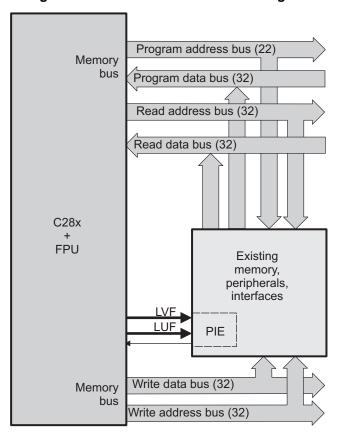

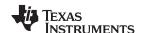

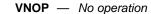

Figure 1-1 shows basic functions of the FPU.

Figure 1-1. FPU Functional Block Diagram

#### 1.1.1.1 Floating-Point Code Development

When developing C28x floating-point code use Code Composer Studio 3.3, or later, with at least service release 8. The C28x compiler V5.0, or later, is also required to generate C28x native floating-point opcodes. This compiler is available via Code Composer Studio update advisor as a seperate download. V5.0 can generate both fixed-point as well as floating-point code. To build floating-point code use the compiler switches:-v28 and - -float\_support = fpu32. In Code Composer Studio 3.3 the float\_support option is in the build options under compiler-> advanced: floating point support. Without the float\_support flag, or with float\_support = none, the compiler will generate fixed-point code.

When building for C28x floating-point make sure all associated libraries have also been built for floating-point. The standard run-time support (RTS) libraries built for floating-point included with the compiler have fpu32 in their name. For example rts2800\_fpu32.lib and rts2800\_fpu\_eh.lib have been built for the floating-point unit. The "eh" version has exception handling for C++ code. Using the fixed-point RTS libraries in a floating-point project will result in the linker issuing an error for incompatible object files.

To improve performance of native floating-point projects, consider using the *C28x FPU Fast RTS Library* (SPRC664). This library contains hand-coded optimized math routines such as division, square root, atan2, sin and cos. This library can be linked into your project before the standard runtime support library to give your application a performance boost. As an example, the standard RTS library uses a polynomial expansion to calculate the sin function. The Fast RTS library, however, uses a math look-up table in the boot ROM of the device. Using this look-up table method results in approximately a 20 cycle savings over the standard RTS calculation.

#### 1.2 Components of the C28x plus Floating-Point CPU

The C28x+FPU contains:

- A central processing unit for generating data and program-memory addresses; decoding and executing instructions; performing arithmetic, logical, and shift operations; and controlling data transfers among CPU registers, data memory, and program memory

- A floating-point unit for IEEE single-precision floating point operations.

- Emulation logic for monitoring and controlling various parts and functions of the device and for testing device operation. This logic is identical to that on the C28x fixed-point CPU.

- Signals for interfacing with memory and peripherals, clocking and controlling the CPU and the

emulation logic, showing the status of the CPU and the emulation logic, and using interrupts. This logic

is identical to the C28x fixed-point CPU.

Some features of the C28x+FPU central processing unit are:

- Fixed-Point instructions are pipeline protected. This pipeline for fixed-point instructions is identical to that on the C28x fixed-point CPU. The CPU implements an 8-phase pipeline that prevents a write to and a read from the same location from occurring out of order. See Figure 1-5.

- Some floating-point instructions require pipeline alignment. This alignment is done through software to allow the user to improve performance by taking advantage of required delay slots.

- Independent register space. These registers function as system-control registers, math registers, and data pointers. The system-control registers are accessed by special instructions.

- Arithmetic logic unit (ALU). The 32-bit ALU performs 2s-complement arithmetic and Boolean logic operations.

- Floating point unit (FPU). The 32-bit FPU performs IEEE single-precision floating-point operations.

- Address register arithmetic unit (ARAU). The ARAU generates data memory addresses and increments or decrements pointers in parallel with ALU operations.

- Barrel shifter. This shifter performs all left and right shifts of fixed-point data. It can shift data to the left by up to 16 bits and to the right by up to 16 bits.

- Fixed-Point Multiplier. The multiplier performs 32-bit × 32-bit 2s-complement multiplication with a 64-bit result. The multiplication can be performed with two signed numbers, two unsigned numbers, or one signed number and one unsigned number.

#### 1.2.1 Emulation Logic

The emulation logic is identical to that on the C28x fixed-point CPU. This logic includes the following features:

- Debug-and-test direct memory access (DT-DMA). A debug host can gain direct access to the content

of registers and memory by taking control of the memory interface during unused cycles of the

instruction pipeline.

- A counter for performance benchmarking.

- Multiple debug events. Any of the following debug events can cause a break in program execution:

- A breakpoint initiated by the ESTOP0 or ESTOP1 instruction.

- An access to a specified program-space or data-space location.

When a debug event causes the C28x to enter the debug-halt state, the event is called a break event.

Real-time mode of operation.

For more details about these features, refer to the *TMS320C28x DSP CPU and Instruction Set Reference Guide* (literature number SPRU430).

#### 1.2.2 Memory Map

Like the C28x, the C28x+FPU uses 32-bit data addresses and 22-bit program addresses. This allows for a total address reach of 4G words (1 word = 16 bits) in data space and 4M words in program space. Memory blocks on all C28x+FPU designs are uniformly mapped to both program and data space. For specific details about each of the map segments, see the data sheet for your device.

#### 1.2.3 On-Chip Program and Data

All C28x+FPU based devices contain at least two blocks of single access on-chip memory referred to as M0 and M1. Each of these blocks is 1K words in size. M0 is mapped at addresses 0x0000 – 0x03FF and M1 is mapped at addresses 0x0400 – 0x07FF. Like all other memory blocks on the C28x+FPU devices, M0 and M1 are mapped to both program and data space. Therefore, you can use M0 and M1 to execute code or for data variables. At reset, the stack pointer is set to the top of block M1. Depending on the device, it may also have additional random-access memory (RAM), read-only memory (ROM), external interface zones, or flash memory.

#### 1.2.4 CPU Interrupt Vectors

The C28x+FPU interrupt vectors are identical to those on the C28x CPU. Sixty-four addresses in program space are set aside for a table of 32 CPU interrupt vectors. The CPU vectors can be mapped to the top or bottom of program space by way of the VMAP bit. For more information about the CPU vectors, see *TMS320C28x DSP CPU and Instruction Set Reference Guide* (literature number SPRU430). For devices with a peripheral interrupt expansion (PIE) block, the interrupt vectors will reside in the PIE vector table and this memory can be used as program memory.

#### 1.2.5 Memory Interface

The C28x+FPU memory interface is identical to that on the C28x. The C28x+FPU memory map is accessible outside the CPU by the memory interface, which connects the CPU logic to memories, peripherals, or other interfaces. The memory interface includes separate buses for program space and data space. This means an instruction can be fetched from program memory while data memory is being accessed. The interface also includes signals that indicate the type of read or write being requested by the CPU. These signals can select a specified memory block or peripheral for a given bus transaction. In addition to 16-bit and 32-bit accesses, the C28x+FPU supports special byte-access instructions that can access the least significant byte (LSByte) or most significant byte (MSByte) of an addressed word. Strobe signals indicate when such an access is occurring on a data bus.

www.ti.com CPU Register Set

#### 1.2.5.1 Address and Data Buses

Like the C28x, the memory interface has three address buses:

#### PAB: Program address bus

The PAB carries addresses for reads and writes from program space. PAB is a 22-bit bus.

#### DRAB: Data-read address bus

The 32-bit DRAB carries addresses for reads from data space.

#### • DWAB: Data-write address bus

The 32-bit DWAB carries addresses for writes to data space.

The memory interface also has three data buses:

#### PRDB: Program-read data bus

The PRDB carries instructions during reads from program space. PRDB is a 32-bit bus.

#### · DRDB: Data-read data bus

The DRDB carries data during reads from data space. DRDB is a 32-bit bus.

#### DWDB: Data-/Program-write data bus

The 32-bit DWDB carries data during writes to data space or program space.

A program-space read and a program-space write cannot happen simultaneously because both use the PAB. Similarly, a program-space write and a data-space write cannot happen simultaneously because both use the DWDB. Transactions that use different buses can happen simultaneously. For example, the CPU can read from program space (using PAB and PRDB), read from data space (using DRAB and DRDB), and write to data space (using DWAB and DWDB) at the same time. This behavior is identical to the C28x CPU.

#### 1.2.5.2 Alignment of 32-Bit Accesses to Even Addresses

The C28x+FPU CPU expects memory wrappers or peripheral-interface logic to align any 32-bit read or write to an even address. If the address-generation logic generates an odd address, the CPU will begin reading or writing at the previous even address. This alignment does not affect the address values generated by the address-generation logic.

Most instruction fetches from program space are performed as 32-bit read operations and are aligned accordingly. However, alignment of instruction fetches are effectively invisible to a programmer. When instructions are stored to program space, they do not have to be aligned to even addresses. Instruction boundaries are decoded within the CPU.

You need to be concerned with alignment when using instructions that perform 32-bit reads from or writes to data space.

#### 1.3 CPU Register Set

The C28x+FPU architecture is the same as the C28x CPU with an extended register and instruction set to support IEEE single-precision floating point operations. This section describes the extensions to the C28x architecture

#### 1.3.1 CPU Registers

Devices with the C28x+FPU include the standard C28x register set plus an additional set of floating-point unit registers. The additional floating-point unit registers are the following:

- Eight floating-point result registers, RnH (where n = 0 7)

- Floating-point Status Register (STF)

- Repeat Block Register (RB)

All of the floating-point registers except the repeat block register are shadowed. This shadowing can be used in high priority interrupts for fast context save and restore of the floating-point registers.

CPU Register Set www.ti.com

Figure 1-2 shows a diagram of both register sets and Table 1-1 shows a register summary. For information on the standard C28x register set, see the *TMS320C28x DSP CPU and Instruction Set Reference Guide* (literature number SPRU430).

Figure 1-2. C28x With Floating-Point Registers

| Ctandard Ozox register Get | _ |  |  |  |  |

|----------------------------|---|--|--|--|--|

| ACC (32-bit)               |   |  |  |  |  |

| P (32-bit)                 |   |  |  |  |  |

| XT (32-bit)                |   |  |  |  |  |

|                            |   |  |  |  |  |

| XAR0 (32-bit)              |   |  |  |  |  |

| XAR1 (32-bit)              |   |  |  |  |  |

| XAR2 (32-bit)              |   |  |  |  |  |

| XAR3 (32-bit)              |   |  |  |  |  |

| XAR4 (32-bit)              |   |  |  |  |  |

| XAR5 (32-bit)              |   |  |  |  |  |

| XAR6 (32-bit)              |   |  |  |  |  |

| XAR7 (32-bit)              |   |  |  |  |  |

|                            |   |  |  |  |  |

| PC (22-bit)                |   |  |  |  |  |

| RPC (22-bit)               |   |  |  |  |  |

| DP (16-bit)                |   |  |  |  |  |

| SP (16-bit)                |   |  |  |  |  |

|                            |   |  |  |  |  |

| ST0 (16-bit)               |   |  |  |  |  |

| ST1 (16-bit)               | 1 |  |  |  |  |

| IER (16-bit)               |   |  |  |  |  |

| IFR (16-bit)               |   |  |  |  |  |

| DBGIER (16-bit)            |   |  |  |  |  |

| ` ′                        |   |  |  |  |  |

Additional 32-bit FPU Registers

| R0H (32-bit)                     |

|----------------------------------|

| R1H (32-bit)                     |

| R2H (32-bit)                     |

| R3H (32-bit)                     |

| R4H (32-bit)                     |

| R5H (32-bit)                     |

| R6H (32-bit)                     |

| R7H (32-bit)                     |

| FPU Status Register (STF)        |

| Repeat Block Register (RB)       |

| EDIT registers ROH - R7H and STE |

FPU registers R0H - R7H and STF are shadowed for fast context save and restore

Copyright © 2014–2019, Texas Instruments Incorporated

www.ti.com CPU Register Set

#### Table 1-1. 28x Plus Floating-Point CPU Register Summary

| Register | C28x CPU | C28x+FPU | Size    | Description                      | Value After Reset     |

|----------|----------|----------|---------|----------------------------------|-----------------------|

| ACC      | Yes      | Yes      | 32 bits | Accumulator                      | 0x0000000             |

| AH       | Yes      | Yes      | 16 bits | High half of ACC                 | 0x0000                |

| AL       | Yes      | Yes      | 16 bits | Low half of ACC                  | 0x0000                |

| XAR0     | Yes      | Yes      | 32 bits | Auxiliary register 0             | 0x0000000             |

| XAR1     | Yes      | Yes      | 32 bits | Auxiliary register 1             | 0x0000000             |

| XAR2     | Yes      | Yes      | 32 bits | Auxiliary register 2             | 0x0000000             |

| XAR3     | Yes      | Yes      | 32 bits | Auxiliary register 3             | 0x0000000             |

| XAR4     | Yes      | Yes      | 32 bits | Auxiliary register 4             | 0x0000000             |

| XAR5     | Yes      | Yes      | 32 bits | Auxiliary register 5             | 0x0000000             |

| XAR6     | Yes      | Yes      | 32 bits | Auxiliary register 6             | 0x0000000             |

| XAR7     | Yes      | Yes      | 32 bits | Auxiliary register 7             | 0x0000000             |

| AR0      | Yes      | Yes      | 16 bits | Low half of XAR0                 | 0x0000                |

| AR1      | Yes      | Yes      | 16 bits | Low half of XAR1                 | 0x0000                |

| AR2      | Yes      | Yes      | 16 bits | Low half of XAR2                 | 0x0000                |

| AR3      | Yes      | Yes      | 16 bits | Low half of XAR3                 | 0x0000                |

| AR4      | Yes      | Yes      | 16 bits | Low half of XAR4                 | 0x0000                |

| AR5      | Yes      | Yes      | 16 bits | Low half of XAR5                 | 0x0000                |

| AR6      | Yes      | Yes      | 16 bits | Low half of XAR6                 | 0x0000                |

| AR7      | Yes      | Yes      | 16 bits | Low half of XAR7                 | 0x0000                |

| DP       | Yes      | Yes      | 16 bits | Data-page pointer                | 0x0000                |

| IFR      | Yes      | Yes      | 16 bits | Interrupt flag register          | 0x0000                |

| IER      | Yes      | Yes      | 16 bits | Interrupt enable register        | 0x0000                |

| DBGIER   | Yes      | Yes      | 16 bits | Debug interrupt enable register  | 0x0000                |

| Р        | Yes      | Yes      | 32 bits | Product register                 | 0x0000000             |

| PH       | Yes      | Yes      | 16 bits | High half of P                   | 0x0000                |

| PL       | Yes      | Yes      | 16 bits | Low half of P                    | 0x0000                |

| PC       | Yes      | Yes      | 22 bits | Program counter                  | 0x3FFFC0              |

| RPC      | Yes      | Yes      | 22 bits | Return program counter           | 0x0000000             |

| SP       | Yes      | Yes      | 16 bits | Stack pointer                    | 0x0400                |

| ST0      | Yes      | Yes      | 16 bits | Status register 0                | 0x0000                |

| ST1      | Yes      | Yes      | 16 bits | Status register 1                | 0x080B <sup>(1)</sup> |

| XT       | Yes      | Yes      | 32 bits | Multiplicand register            | 0x0000000             |

| Т        | Yes      | Yes      | 16 bits | High half of XT                  | 0x0000                |

| TL       | Yes      | Yes      | 16 bits | Low half of XT                   | 0x0000                |

| ROH      | No       | Yes      | 32 bits | Floating-point result register 0 | 0.0                   |

| R1H      | No       | Yes      | 32 bits | Floating-point result register 1 | 0.0                   |

| R2H      | No       | Yes      | 32 bits | Floating-point result register 2 | 0.0                   |

| R3H      | No       | Yes      | 32 bits | Floating-point result register 3 | 0.0                   |

| R4H      | No       | Yes      | 32 bits | Floating-point result register 4 | 0.0                   |

| R5H      | No       | Yes      | 32 bits | Floating-point result register 5 | 0.0                   |

| R6H      | No       | Yes      | 32 bits | Floating-point result register 6 | 0.0                   |

| R7H      | No       | Yes      | 32 bits | Floating-point result register 7 | 0.0                   |

| STF      | No       | Yes      | 32 bits | Floating-point status register   | 0x00000000            |

| RB       | No       | Yes      | 32 bits | Repeat block register            | 0x0000000             |

<sup>(1)</sup> Reset value shown is for devices without the VMAP signal and MOM1MAP signal pinned out. On these devices both of these signals are tied high internal to the device.

CPU Register Set www.ti.com

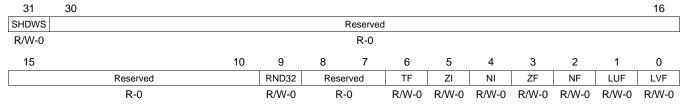

#### 1.3.1.1 Floating-Point Status Register (STF)

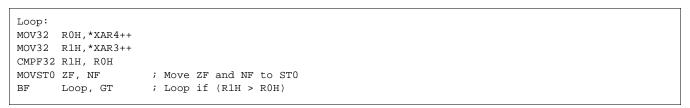

The floating-point status register (STF) reflects the results of floating-point operations. There are three basic rules for floating point operation flags:

- 1. Zero and negative flags are set based on moves to registers.

- 2. Zero and negative flags are set based on the result of compare, minimum, maximum, negative and absolute value operations.

- 3. Overflow and underflow flags are set by math instructions such as multiply, add, subtract and 1/x. These flags may also be connected to the peripheral interrupt expansion (PIE) block on your device. This can be useful for debugging underflow and overflow conditions within an application.

As on the C28x, program flow is controlled by C28x instructions that read status flags in the status register 0 (ST0). If a decision needs to be made based on a floating-point operation, the information in the STF register needs to be loaded into ST0 flags (Z,N,OV,TC,C) so that the appropriate branch conditional instruction can be executed. The MOVST0 FLAG instruction is used to load the current value of specified STF flags into the respective bits of ST0. When this instruction executes, it will also clear the latched overflow and underflow flags if those flags are specified.

#### Example 1-1. Moving STF Flags to the ST0 Register

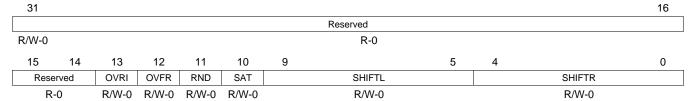

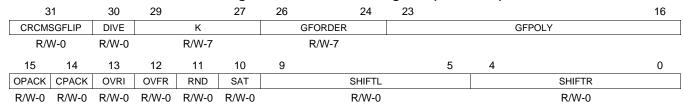

#### Figure 1-3. Floating-point Unit Status Register (STF)

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 1-2. Floating-point Unit Status (STF) Register Field Descriptions

| Bits    | Field    | Value | Description                                                                                                                                       |  |  |

|---------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 31      | SHDWS    |       | Shadow Mode Status Bit                                                                                                                            |  |  |

|         |          | 0     | This bit is forced to 0 by the RESTORE instruction.                                                                                               |  |  |

|         |          | 1     | This bit is set to 1 by the SAVE instruction.                                                                                                     |  |  |

|         |          |       | This bit is not affected by loading the status register either from memory or from the shadow values.                                             |  |  |

| 30 - 10 | Reserved | 0     | Reserved for future use                                                                                                                           |  |  |

| 9       | RND32    |       | Round 32-bit Floating-Point Mode                                                                                                                  |  |  |

|         |          | 0     | If this bit is zero, the MPYF32, ADDF32 and SUBF32 instructions will round to zero (truncate).                                                    |  |  |

|         |          | 1     | If this bit is one, the MPYF32, ADDF32 and SUBF32 instructions will round to the nearest even value.                                              |  |  |

| 8 - 7   | Reserved | 0     | Reserved for future use                                                                                                                           |  |  |

| 6       | TF       |       | Test Flag                                                                                                                                         |  |  |

|         |          |       | The TESTTF instruction can modify this flag based on the condition tested. The SETFLG and SAVE instructions can also be used to modify this flag. |  |  |

|         |          | 0     | The condition tested with the TESTTF instruction is false.                                                                                        |  |  |

|         |          | 1     | The condition tested with the TESTTF instruction is true.                                                                                         |  |  |

www.ti.com CPU Register Set

### Table 1-2. Floating-point Unit Status (STF) Register Field Descriptions (continued)

| Bits | Field | Value | Description                                                                                                                                                                                                                                                                                                                         |  |  |  |

|------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 5    | ZI    |       | Zero Integer Flag                                                                                                                                                                                                                                                                                                                   |  |  |  |

|      |       |       | The following instructions modify this flag based on the integer value stored in the destination register: MOV32, MOVD32, MOVD32  The SETFLG and SAVE instructions can also be used to modify this flag.                                                                                                                            |  |  |  |

|      |       | 0     | The integer value is not zero.                                                                                                                                                                                                                                                                                                      |  |  |  |

|      |       | 1     | The integer value is zero.                                                                                                                                                                                                                                                                                                          |  |  |  |

| 4    | NI    |       | Negative Integer Flag                                                                                                                                                                                                                                                                                                               |  |  |  |

|      |       |       | The following instructions modify this flag based on the integer value stored in the destination register: MOV32, MOVD32, MOVD32  The SETFLG and SAVE instructions can also be used to modify this flag.                                                                                                                            |  |  |  |

|      |       | 0     | The integer value is not negative.                                                                                                                                                                                                                                                                                                  |  |  |  |

|      |       | 1     | The integer value is negative.                                                                                                                                                                                                                                                                                                      |  |  |  |

| 3    | ZF    |       | Zero Floating-Point Flag (1) (2)                                                                                                                                                                                                                                                                                                    |  |  |  |

|      |       |       | The following instructions modify this flag based on the floating-point value stored in the destination register:  MOV32, MOVD32, MOVD32, ABSF32, NEGF32  The CMPF32, MAXF32, and MINF32 instructions modify this flag based on the result of the operation.  The SETFLG and SAVE instructions can also be used to modify this flag |  |  |  |

|      |       | 0     | The floating-point value is not zero.                                                                                                                                                                                                                                                                                               |  |  |  |

|      |       | 1     | The floating-point value is zero.                                                                                                                                                                                                                                                                                                   |  |  |  |

| 2    | NF    |       | Negative Floating-Point Flag (1) (2)                                                                                                                                                                                                                                                                                                |  |  |  |

|      |       |       | The following instructions modify this flag based on the floating-point value stored in the destination register: MOV32, MOVD32, MOVDD32, ABSF32, NEGF32 The CMPF32, MAXF32, and MINF32 instructions modify this flag based on the result of the operation. The SETFLG and SAVE instructions can also be used to modify this flag.  |  |  |  |

|      |       | 0     | The floating-point value is not negative.                                                                                                                                                                                                                                                                                           |  |  |  |

|      |       | 1     | The floating-point value is negative.                                                                                                                                                                                                                                                                                               |  |  |  |

| 1    | LUF   |       | Latched Underflow Floating-Point Flag                                                                                                                                                                                                                                                                                               |  |  |  |

|      |       |       | The following instructions will set this flag to 1 if an underflow occurs: MPYF32, ADDF32, SUBF32, MACF32, EINVF32, EISQRTF32                                                                                                                                                                                                       |  |  |  |

|      |       | 0     | An underflow condition has not been latched. If the MOVST0 instruction is used to copy this bit to ST0, then LUF will be cleared.                                                                                                                                                                                                   |  |  |  |

|      |       | 1     | An underflow condition has been latched.                                                                                                                                                                                                                                                                                            |  |  |  |

| 0    | LVF   |       | Latched Overflow Floating-Point Flag                                                                                                                                                                                                                                                                                                |  |  |  |

|      |       |       | The following instructions will set this flag to 1 if an overflow occurs: MPYF32, ADDF32, SUBF32, MACF32, EINVF32, EISQRTF32                                                                                                                                                                                                        |  |  |  |

|      |       | 0     | An overflow condition has not been latched. If the MOVST0 instruction is used to copy this bit to ST0, then LVF will be cleared.                                                                                                                                                                                                    |  |  |  |

|      |       | 1     | An overflow condition has been latched.                                                                                                                                                                                                                                                                                             |  |  |  |

<sup>&</sup>lt;sup>(1)</sup> A negative zero floating-point value is treated as a positive zero value when configuring the ZF and NF flags.

<sup>(2)</sup> A DeNorm floating-point value is treated as a positive zero value when configuring the ZF and NF flags.

CPU Register Set www.ti.com

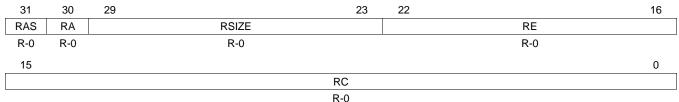

#### 1.3.1.2 Repeat Block Register (RB)

The repeat block instruction (RPTB) is a new instruction for C28x+FPU. This instruction allows you to repeat a block of code as shown in Example 1-2.

#### Example 1-2. The Repeat Block (RPTB) Instruction uses the RB Register

```

; find the largest element and put its address in XAR6

MOV32 ROH, *XAR0++;

.align 2

; Aligns the next instruction to an even address

NOP

; Makes RPTB odd aligned - required for a block size of 8

; RA is set to 1

RPTB

VECTOR_MAX_END, AR7

MOVL

ACC, XARO

R1H,*XAR0++

; RSIZE reflects the size of the RPTB block

MOV32

MAXF32 ROH,R1H

; in this case the block size is 8

MOVSTO NF, ZF

XAR6,ACC,LT

TVOM.

VECTOR_MAX_END:

; RE indicates the end address. RA is cleared

```

The C28x\_FPU hardware automatically populates the RB register based on the execution of a RPTB instruction. This register is not normally read by the application and does not accept debugger writes.

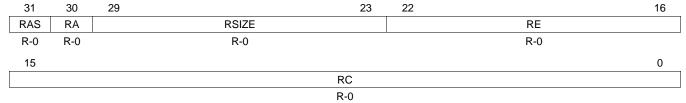

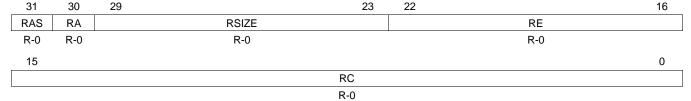

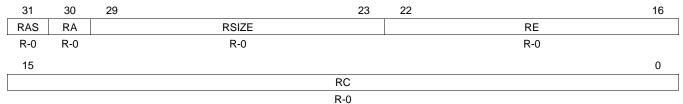

### Figure 1-4. Repeat Block Register (RB)

LEGEND: R = Read only; -n = value after reset

#### Table 1-3. Repeat Block (RB) Register Field Descriptions

| Bits  | Field | Value    | Description                                                                                                                                                                                                                                                                        |  |  |  |

|-------|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 31    | RAS   |          | Repeat Block Active Shadow Bit                                                                                                                                                                                                                                                     |  |  |  |

|       |       |          | When an interrupt occurs the repeat active, RA, bit is copied to the RAS bit and the RA bit is cleared. When an interrupt return instruction occurs, the RAS bit is copied to the RA bit and RAS is cleared.                                                                       |  |  |  |

|       |       | 0        | repeat block was not active when the interrupt was taken.                                                                                                                                                                                                                          |  |  |  |

|       |       | 1        | A repeat block was active when the interrupt was taken.                                                                                                                                                                                                                            |  |  |  |

| 30    | RA    |          | Repeat Block Active Bit                                                                                                                                                                                                                                                            |  |  |  |

|       |       | 0        | This bit is cleared when the repeat counter, RC, reaches zero.                                                                                                                                                                                                                     |  |  |  |

|       |       |          | Then an interrupt occurs the RA bit is copied to the repeat active shadow, RAS, bit and RA is cleared. Then an interrupt return, IRET, instruction is executed, the RAS bit is copied to the RA bit and RAS is eared.                                                              |  |  |  |

|       |       | 1        | This bit is set when the RPTB instruction is executed to indicate that a RPTB is currently active.                                                                                                                                                                                 |  |  |  |

| 29-23 | RSIZE |          | Repeat Block Size                                                                                                                                                                                                                                                                  |  |  |  |

|       |       |          | his 7-bit value specifies the number of 16-bit words within the repeat block. This field is initialized then the RPTB instruction is executed. The value is calculated by the assembler and inserted into the PTB instruction's RSIZE opcode field.                                |  |  |  |

|       |       | 0-7      | egal block size.                                                                                                                                                                                                                                                                   |  |  |  |

|       |       | 8/9-0x7F | A RPTB block that starts at an even address must include at least 9 16-bit words and a block that starts at an odd address must include at least 8 16-bit words. The maximum block size is 127 16-bit words. The codegen assembler will check for proper block size and alignment. |  |  |  |

www.ti.com Pipeline

| Table 1-3. Repeat Block | (RB)  | Register Field Descrip  | otions (continue  | (be |

|-------------------------|-------|-------------------------|-------------------|-----|

| rabio i di Nopoat Biook | (., - | regiotor i loia booorij | sticile (continue | ,,, |

| Bits  | Field | Value        | Description                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-------|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 22-16 | RE    |              | Repeat Block End Address                                                                                                                                                                                                                                                                                                                                                          |  |  |

|       |       |              | is 7-bit value specifies the end address location of the repeat block. The RE value is calculated by rdware based on the RSIZE field and the PC value when the RPTB instruction is executed.                                                                                                                                                                                      |  |  |

|       |       |              | RE = lower 7 bits of (PC + 1 + RSIZE)                                                                                                                                                                                                                                                                                                                                             |  |  |

| 15-0  | RC    |              | Repeat Count                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|       |       | 0            | The block will not be repeated; it will be executed only once. In this case the repeat active, RA, bit will not be set.                                                                                                                                                                                                                                                           |  |  |

|       |       | 1-<br>0xFFFF | This 16-bit value determines how many times the block will repeat. The counter is initialized when the RPTB instruction is executed and is decremented when the PC reaches the end of the block. When the counter reaches zero, the repeat active bit is cleared and the block will be executed one more time. Therefore the total number of times the block is executed is RC+1. |  |  |

#### 1.4 Pipeline

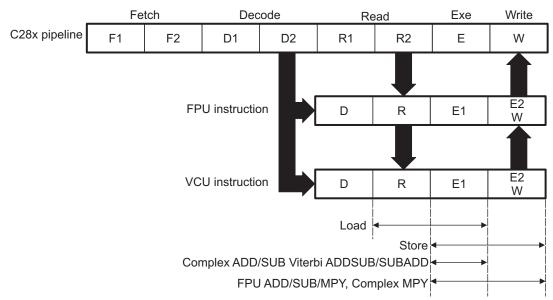

The pipeline flow for C28x instructions is identical to that of the C28x CPU described in *TMS320C28x DSP CPU and Instruction Set Reference Guide* (SPRU430). Some floating-point instructions, however, use additional execution phases and thus require a delay to allow the operation to complete. This pipeline alignment is achieved by inserting NOPs or non-conflicting instructions when required. Software control of delay slots allows you to improve performance of an application by taking advantage of the delay slots and filling them with non-conflicting instructions. This section describes the key characteristics of the pipeline with regards to floating-point instructions. The rules for avoiding pipeline conflicts are small in number and simple to follow and the C28x+FPU assembler will help you by issuing errors for conflicts.

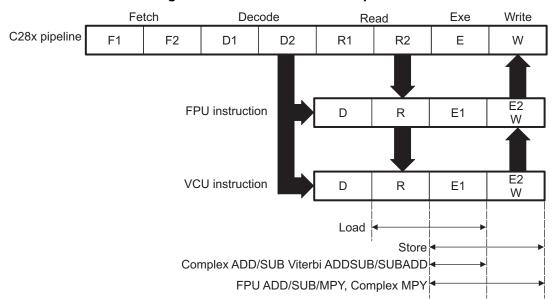

#### 1.4.1 Pipeline Overview

The C28x FPU pipeline is identical to the C28x pipeline for all standard C28x instructions. In the decode2 stage (D2), it is determined if an instruction is a C28x instruction or a floating-point unit instruction. The pipeline flow is shown in Figure 1-5. Notice that stalls due to normal C28x pipeline stalls (D2) and memory waitstates (R2 and W) will also stall any C28x FPU instruction. Most C28x FPU instructions are single cycle and will complete in the FPU E1 or W stage which aligns to the C28x pipeline. Some instructions will take an additional execute cycle (E2). For these instructions you must wait a cycle for the result from the instruction to be available. The rest of this section will describe when delay cycles are required. Keep in mind that the assembly tools for the C28x+FPU will issue an error if a delay slot has not been handled correctly.

Fetch Decode Exe Write Read C28x pipeline F1 F2 D1 D2 R1 R2 Ε W F2 **FPU** instruction D R E1 Load Store CMP/MIN/MAX/NEG/ABS MPY/ADD/SUB/MACF32

Figure 1-5. FPU Pipeline

Pipeline www.ti.com

#### 1.4.2 General Guidelines for Floating-Point Pipeline Alignment

While the C28x+FPU assembler will issue errors for pipeline conflicts, you may still find it useful to understand when software delays are required. This section describes three guidelines you can follow when writing C28x+FPU assembly code.

Floating-point instructions that require delay slots have a 'p' after their cycle count. For example '2p' stands for 2 pipelined cycles. This means that an instruction can be started every cycle, but the result of the instruction will only be valid one instruction later.

There are three general guidelines to determine if an instruction needs a delay slot:

- 1. Floating-point math operations (multiply, addition, subtraction, 1/x and MAC) require 1 delay slot.

- 2. Conversion instructions between integer and floating-point formats require 1 delay slot.

- 3. Everything else does not require a delay slot. This includes minimum, maximum, compare, load, store, negative and absolute value instructions.