# Adjustable Current Limit of Smart Power Switches

Shreyas Dmello, Alec Forbes, Alex Wang and Alvin Xu

#### **ABSTRACT**

During inrush or fault situations, traditional high side switches have very high current limits that are designed to accommodate all load requirements, but provide only limited system protection. To improve system reliability, TI Smart Power Switches provide an adjustable low current limit that decreases fault energy during fault cases and increases system lifetime reliability. The adjustable current limit can be used to clamp overload current, deliver constant current, control inrush current and reduce the amount of current flow during short to ground events. This can result in lower system costs by reducing the size of passive components, cables, connectors and PCB traces. An accurate and appropriately chosen current limit overall increases system reliability during both standard operation as well as during fault cases to ensure a long product lifetime.

This application report introduces the principles and advantages of the adjustable current limiting before guiding the user through selecting and implementing the adjustable current limit value. The document will then provide examples discussing how to leverage this feature for different application scenarios to provide the highest system reliability.

#### **Contents** Introduction 3 2 3 4 Current Limit Accuracy 8 5 6 **List of Figures** 1 3 5 6 Comparison of Different Current Limit Accuracy 9 7 Current Creep Behavior......9 8 10 11 12 13 14 Using Smart Power Switch as Inrush Current Clamper in Infotainment System ...... 14 15 16 17 18

| www.ti.com                                                |    |

|-----------------------------------------------------------|----|

| 9 Hard Short Current Waveform 16                          | 19 |

| 20 Dynamic Current Limit Control                          | 20 |

| 21 External Circuitry of Dynamic Current Limit Control    | 21 |

| List of Tables                                            |    |

| Fault Energy Calculation4                                 | 1  |

| 2 TPSxHxxx Current Limit Specifications Summary           | 2  |

| TPSxHBxx Current Limit Specifications Summary             | 3  |

| Current Limit Accuracy Summary of TPSxHxxx Family Devices | 4  |

## **Trademarks**

All trademarks are the property of their respective owners.

www.ti.com Introduction

#### 1 Introduction

Smart Power Switches from Texas Instruments are robust automotive-grade power switches with a wide range of on-resistances and channel count configurations. The devices offer protection against short to ground and overload events through adjustable over-current protection. This increases system design flexibility by allowing the user to select a current limit value that meets the system requirements, improving the reliability of the whole system by limiting the overload current and preventing the front stage power budget from designing in large margins to handle overload and fault conditions. By ensuring low fault current, the system can have decreased PCB trace wdiths and cable sizes lowering the overall system cost and size.

Texas Instruments offers Smart Power Switch current limiting solutions in both a load current clamping and instant shutdown version. This versatility allows for these switches to be used in applications that involve frequent high current events that need to be clamped as well as applications with sensitive loads that need to be quickly protected in the event of a short.

Smart Power Switch offerings from TI combine these benefits with a low on-resistance. This allows small integrated designs to be used for high power and high load current applications, and due to the low power dissipation the system thermal efficiency is improved. In addition to current limiting, the device provides high-accuracy current sense and enables full diagnostics and intelligent control of the load.

#### 2 **Advantages of Adjustable Current Limiting**

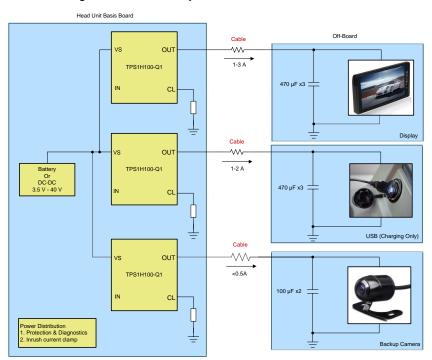

High side switches are required in a wide variety of automotive and industrial applications where power must be provided to off-board loads. Figure 1 shows a few standard automotive loads where power must be delivered from a standard automotive electronic control unit (ECU) to a separate module, each of which requires protection and diagnostic functionality.

Figure 1. Automotive Smart Power Switch Applications

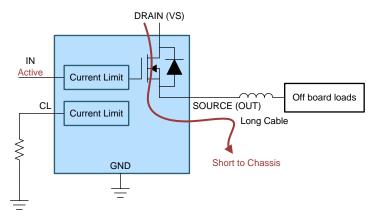

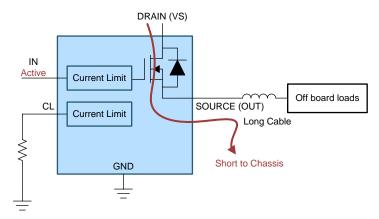

In each of these applications, one of the primary concerns is a short circuit from the output to GND as shown in Figure 2. In the event a short-circuit occurs, the high side switch is responsible for monitoring the current and preventing damage to the system by shutting off output power.

Figure 2. Short Circuit Event

To protect the system, an ideal high side switch will quickly shut off current flow during a short circuit event, limiting the peak current to a low safe level. If the current gets to a high level before the high side switch shuts down the system, this introduces additional fault energy into the system that can charge inductors, heat up components, and overload traces and connectors.

During a short circuit, any output cable inductance will be charged up due to the current flow, creating additional energy stored in the system. Equation 1 calculates the energy stored in cable inductance, which is proportional to square of the fault current.

$$P_{\text{FAULT}} = 0.5 * L_{\text{OUT}} * I_{\text{FAULT}}^2 \tag{1}$$

When the high side switch shuts off, the system might see failures when dissipating this stored inductive energy. To limit the energy that must be dissipated in the system and increase system reliability, the biggest impact can be had by lowering  $I_{\text{FAULT}}$ . Through use of an **adjustable current limit**, the peak fault current can be significantly lowered, removing current limiting margin that is a downside of standard high side switches. This decreases the maximum possible output current, and consequently significantly lowers the fault power and energy during a short circuit event.

TI Smart Power Switches current limit range vary but are always possible to set below 10 A, much lower than traditional switches. Table 1 compares the TPS2HB08-Q1 to a comparable traditional high side switch which has a nominal current limit of around 75 A, and uses Equation 1 to show that a system using the TPS2HB08-Q1 will see 8.5% of the maximum fault current and 0.7 % of the maximum fault energy compared to a system using a traditional high side switch.

Device Current Limit (I<sub>LIM</sub>) Energy in a 5 μH cable

Table 1. Fault Energy Calculation

6.4 A

75 A

If a short-circuit occurs repetitively, the high side switch must continually dissipate this 14 mJ which can damage the lifetime of the switch. Lowering the current limit lowers the repetitive energy dissipation and prevents damage to the system.

In addition, the lower current limit lowers overall system costs. A partial output short could draw up to the current limit without tripping, so using a traditional high side switch there is the risk that the output could draw a continuous 75 A current that the system must be able to handle. This means having larger traces, components, power supplies, and cables, directly translating to higher system costs and sizes. A system using the TPS2HB08-Q1, however, can ensure that the system will never draw a current greater than 6.4 A, so the system can be designed more efficiently around this maximum current value, saving costs.

TPS2HB08-Q1

Traditional High Side Switch

0.1 mJ

14 mJ

#### 3 Adjustable Current Limit Description

TI Smart Power Switches that include an adjustable current limit are broadly divided into the TPSxHxxx and the TPSxHBxx family of devices. Both families have similar functionality with respect to their adjustable current limits and provide similar protective benefits but differ in the on-resistance range offered. The TPSxHxxx devices are offered with higher on-resistance and are preferred for lower power loads while the TPSxHBxx family is offered with low on-resistance for high power loads. One key difference between these families is the implementation of the external current limit.

#### 3.1 Basic Implementation for TPSxHxxx Devices

The TPSxHxxx devices have two different current-limit modes. When the CL pin is tied to GND, the device references the internal current limit mode. When tied through a resistor  $R_{(CL)}$  to GND, the device enters external current limit mode. The external adjustable current limit allows the flexibility to set the current limit value for different applications.

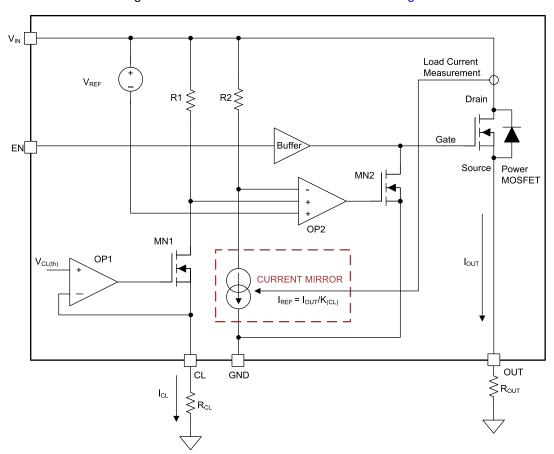

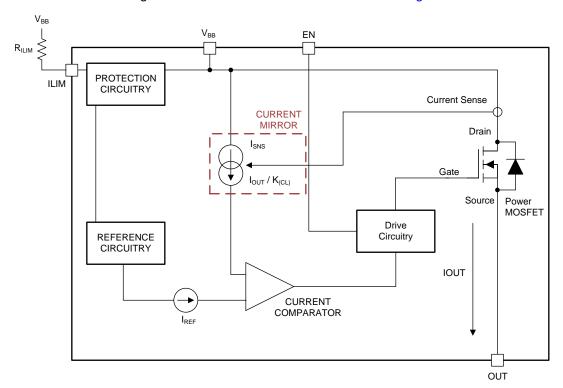

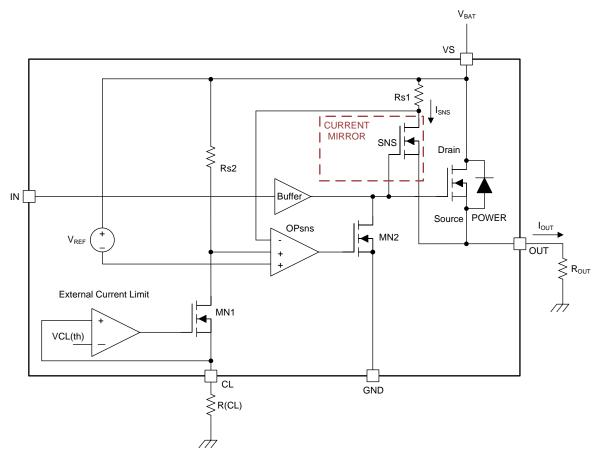

The current limit block diagram for the TPSxHxxx devices is shown in Figure 3.

Figure 3. TPSxHxxx Internal Block Diagram of Current Limit

Using a high accuracy current sense mirror, the output current  $I_{OUT}$  is stepped down to create an internal reference  $I_{REF}$  as shown in Equation 2.

$$I_{REF} = I_{OUT} / K_{(CL)}$$

(2)

$K_{(CL)}$  is the constant ratio of the output current  $I_{OUT}$  and the reference current  $I_{REF}$  and is found in the device electrical characteristics table. This ratio is dependant on the electrical and physical properties of the current mirror and cannot be modified by the user.

The reference current  $I_{REF}$  creates a voltage drop  $V_{R2}$  over  $R_2$  that is proportional to  $I_{OUT}$ , as shown in Equation 3:

$$V_{R2} = I_{REF} \times R_2 \tag{3}$$

V<sub>R2</sub> is proportional to I<sub>OUT</sub> and serves as the basis of the current limiting circuitry. It is referenced by the inverting terminal of the op-amp OP2 against the user set current limit. Depending on whether there is a resistor on the CL pin, the device will use one or the other of the non-inverting terminals.

When there is **no resistor on the CL pin**, the device uses the internal fixed current limit and compares  $V_{R2}$  with the internal reference voltage  $V_{REF}$ . This internal reference voltage is responsible for setting the current limit to the internal pre-set current limit. This value will always be higher than the external set current limit, so will not be a factor if there is a resistor on the CL pin.

When there is a resistor  $R_{\text{CL}}$  on the CL pin, the external adjustable current limit voltage is set by the value of  $R_{\text{CL}}$  and is maintained by OP1 and MN1. The  $R_{\text{CL}}$  value determines the current through the CL pin and is calculated in Equation 6.

$$I_{CL} = V_{CL(th)} / R_{CL} \tag{4}$$

$V_{\text{CL(th)}}$  is the internal band gap voltage that is created by OP1 and MN1 and is defined in the device electrical characteristics table. Because  $R_1$  is equal to  $R_2$ , the voltage drop  $V_{R1}$  can be calculated as shown in Equation 5.

$$V_{R1} = I_{CL} \times R_1 = I_{CL} \times R_2$$

(5)

$V_{R1}$  is tied to one of the non-inverting terminals of OP2 and compared to the  $V_{R2}$  value created by the internal reference  $I_{REF}$ . When the output current  $I_{OUT}$  increases so that  $V_{R2}$  surpasses  $V_{R1}$ , then OP2 regulates  $V_{R2}$  such that it equals  $V_{R1}$ . We can then calculate the clamped output current  $I_{OUT}$  from Equation 2 and Equation 3

$$I_{OUT} = I_{REF} \times K_{CL} = (V_{R2} / R_2) \times K_{CL}$$

$$(6)$$

Because  $V_{R2}$  is being regulated to equal  $V_{R1}$ , we can substitute in Equation 5 and Equation 4 to get a final value for  $I_{OUT}$  in current limiting mode.

$$I_{\text{OUT}} = I_{\text{CL}} \times K_{\text{CL}} = \left(V_{\text{CL}(\text{th})} / R_{\text{CL}}\right) \times K_{\text{CL}} \tag{7}$$

Therefore, the output current limit is set as shown in Equation 8, where  $R_{CL}$  is the current limiting resistor on the CL pin in ohms,  $K_{CL}$  is the internal current divider, and  $V_{CL(th)}$  is the internal bandgap reference. Both  $K_{CL}$  and  $V_{CL(th)}$  are internally fixed in the device, but  $R_{CL}$  can be shifted to set  $I_{OUT}$  to the desired current limit

$$I_{\text{OUT}} = (V_{\text{CL}(\text{th})} / R_{\text{CL}}) \times K_{\text{CL}}$$

(8)

When  $I_{OUT}$  exceeds the current limit, the Power MOSFET changes from linear mode to saturation mode. This increases the voltage drop over the MOSFET and therefore increases the power dissipation, which must be considered during the system level design. The voltage drop over the Power MOSFET  $V_{DS}$  is shown in Equation 9.

$$V_{DS} = V_{IN} - V_{OUT} = V_{IN} - (I_{OUT} \times R_{OUT})$$

$$(9)$$

During current limiting,  $I_{OUT}$  is regulated at  $I_{CL}$ so this and Equation 9 can be used to calculate the power dissipation  $P_{DS}$  in the Power MOSFET during current limiting.

$$P_{DS} = V_{DS} \times I_{CL} = (V_{IN} - (I_{CL} * R_{OUT})) \times I_{CL}$$

(10)

Because current limiting mode typically occurs during a short circuit or inrush situation where  $R_{OUT}$  is very small,  $P_{DS}$  can be approximated as shown in Equation 11.

$$P_{DS} \approx V_{IN} \times I_{CL} \tag{11}$$

Therefore, a high input voltage supply or current limit can cause very high power dissipation in the high side switch during current limiting. If this power dissipated in the switch causes the operating temperature to rise above the thermal shutdown threshold  $T_{\text{SD}}$  then the switch will turn off to protect itself and the load further downstream. If it is desired that the high side switch maintains the output current at  $I_{\text{CL}}$  for longer, then  $I_{\text{CL}}$  should be set at a lower level.

Table 2 gives a summary of the TPSxHxxx devices at 25°C.

Table 2. TPSxHxxx Current Limit Specifications Summary

| Part Number | External Current Limit | Internal Current Limit (Nominal) | V <sub>CL(th)</sub> | K <sub>(CL)</sub> |

|-------------|------------------------|----------------------------------|---------------------|-------------------|

| TPS1H100-Q1 | 0.5 A - 7 A            | 10 A                             | 1.233 V             | 2000              |

| TPS27S100   | 0.5 A - 7 A            | 10 A                             | 1.233 V             | 2000              |

| Part Number | External Current Limit | Internal Current Limit<br>(Nominal) | $V_{\text{CL(th)}}$ | K <sub>(CL)</sub> |

|-------------|------------------------|-------------------------------------|---------------------|-------------------|

| TPS2H160-Q1 | 0.25 A - 9 A           | 12 A                                | 0.8 V               | 2500              |

| TPS4H160-Q1 | 0.25 A - 8 A           | 11 A                                | 0.8 V               | 2500              |

| TPS1H200-Q1 | 0.25 A - 4 A           | 4.8 A                               | 0.8 V               | 2500              |

| TPS1H000-Q1 | 50 mA - 1 A            | 1.4A                                | 0.8 V               | 600               |

| TPS2H000-Q1 | 50 mA - 1 A            | 1.3 A                               | 0.8 V               | 300               |

| TPS4H000-Q1 | 50 mA - 1 A            | 1.3 A                               | 0.8 V               | 300               |

Table 2. TPSxHxxx Current Limit Specifications Summary (continued)

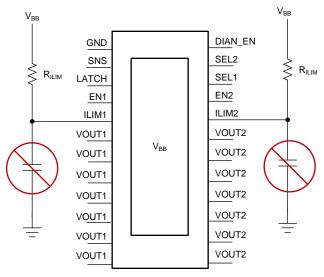

## 3.2 Basic Implementation for TPSxHBxx Devices

The TPSxHBxx devices also have an adjustable current limit that is set by placing an  $R_{\rm ILIM}$  between the supply and the ILIM pin. In these devices, there is a defined  $R_{\rm ILIM}$  range in the datasheet. If the  $R_{\rm ILIM}$  is outside of this range, the device will default back to a higher internal current limit so that the system has some protection, however an  $R_{\rm ILIM}$  resistor is required. When the ILIM pin is connected to the voltage supply rail through a current limiting resistor, the accurate external current limit reference allows for the TPSxHBxx family of devices to be used in applications where load protection is paramount.

Some devices in the TPSxHBxx family include a device version F. In these devices, there is no externally adjustable current limit and the device only includes a fixed internal current reference. In this case, the devices do not have a ILIM pin.

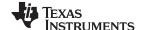

The current limit block diagram for the TPSxHBxx devices is shown in Figure 4.

Figure 4. TPSxHBxx Internal Block Diagram of Current Limit

Through the high accuracy current monitor, the sense current is defined by Equation 12.  $K_{CL}$  is the constant ratio between the output current and the current through the mirror. It is defined by electrical characteristics of the device and cannot be modified by the user.

$$I_{SNS} = I_{OUT} \div K_{CL} \tag{12}$$

Current Limit Accuracy www.ti.com

With a resistor on the ILIM pin, the external current limit mode is determined by the user with Equation 13.  $K_{CL}$  is defined such that the value of  $R_{ILIM}$  is in  $k\Omega$ .

$$I_{\text{LIM}} = K_{\text{CL}} \div R_{\text{ILIM}} \tag{13}$$

Internal to the device, there is a current limit reference switch circuit which confirms if the external current limiting resistor is in the allowed  $R_{\text{ILIM}}$  range from the datasheet. If compliant, the external current limit reference set by the user is set as the current limit. If not compliant, then the internal current limit reference is set as the current limit for the switch.

Irrespective of which reference is chosen, the voltage on the ILIM pin should be as stable as possible for the current limit to not vary when the device is in use. Parasitic capacitance between this pin and the external system must be minimized to mitigate any voltage variation on this pin as shown in Figure 5. This can be done by minimizing the trace length between the pin, current limiting resistor and  $V_{BB}$  supply rail. It is also recommended that a layer cutout on the PCB is implemented below any trace of the current limiting circuitry.

Figure 5. TPS2HB08-Q1 Current Limit Circuitry Example

Table 3 shows a quick summary for TPSxHBxx devices at 25°C. This table has the allowed external current limit range calculated from Equation 13 by using the compatible  $R_{\text{ILIM}}$  range and the  $K_{\text{CL}}$  stated on the datasheet of these devices. It also includes the limits for all the versions offered.

| Part Number | External Current Limit Range                         | R <sub>ILIM</sub> Range | K <sub>CL</sub>                    | Internal Current Limit |

|-------------|------------------------------------------------------|-------------------------|------------------------------------|------------------------|

| TPS2HB50-Q1 | 1.6 A - 8 A (Version A)<br>4.4 A - 22 A (Version B)  | 5-25 kΩ                 | 40 (Version A)<br>110 (Version B)  | 29 A                   |

| TPS2HB35-Q1 | 2 A - 10 A (Version A)<br>6 A - 30 A (Version B)     | 5-25 kΩ                 | 50 (Version A)<br>150 (Version B)  | 42 A                   |

| TPS2HB16-Q1 | 4.4 A - 22 A (Version A)<br>9.8 A - 49 A (Version B) | 5-25 kΩ                 | 110 (Version A)<br>245 (Version B) | 66 A                   |

| TPS2HB08-Q1 | 6.4 A - 32 A (Version A)<br>14 A - 70 A (Version B)  | 5-25 kΩ                 | 160 (Version A)<br>350 (Version B) | 94 A                   |

Table 3. TPSxHBxx Current Limit Specifications Summary

# 4 Current Limit Accuracy

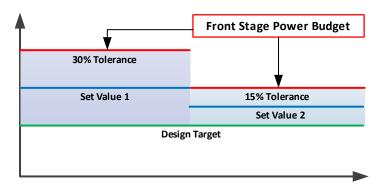

Besides the current limit threshold, the current limit accuracy also should be taken into consideration during system level design. Figure 6 shows the relationship of the design target (Green Line), set value (Blue Line) and the front stage power budget (Red Line). From the ±30% and ±15% tolerance comparison, it is clear that a higher accuracy means a lower front stage power budget.

www.ti.com Current Limit Accuracy

Figure 6. Comparison of Different Current Limit Accuracy

Table 4 shows the accuracy for each device in different current limit range. All the data are across the full temperature range. For detailed information, see the device-specific data sheet.

| Part Number                               | Current Limit Range | Current Limit Accuracy |

|-------------------------------------------|---------------------|------------------------|

| TPS1H100-Q1<br>TPS27S100                  | 0.5 A - 1.6 A       | ≤ ±20%                 |

|                                           | 1.6 A - 7 A         | ≤ ±14%                 |

| TPS2H160-Q1                               | 0.25 A - 0.5 A      | ≤ ±20%                 |

| TPS4H160-Q1                               | 0.5 A - 7 A         | ≤ ±15%                 |

| TPS1H200-Q1                               | 0.25 A - 0.5 A      | ≤ ±20%                 |

|                                           | 0.5 A - 1.5 A       | ≤ ±15%                 |

| TPS1H000-Q1<br>TPS2H000-Q1<br>TPS4H000-Q1 | 0.05 A - 0.1 A      | ≤ ±25%                 |

|                                           | 0.1 A - 0.2 A       | ≤ ±20%                 |

|                                           | 0.2 A - 0.5 A       | ≤ ±15%                 |

|                                           | 0.5 A - 0.9 A       | ≤ ±10%                 |

Table 4. Current Limit Accuracy Summary of TPSxHxxx Family Devices

# 4.1 TPSxHxxx Current Limiting Accuracy during Current Creep

The current limiting accuracy for TPSxHxxx devices is different between instantaneous over-current events and slow current creeping events. Current creeping is defined as a fault that results in the slow increment of load current from a normal operating level to the set current limit. It does not affect the lower on resistance TPSxHBxx devices due to differences between the device architectures. Due to the electrical characteristics of the sense FET in the current mirroring circuitry of the affected devices, the ratio of the load current to the mirrored current is only defined while the FET is in its saturation region. The drain to source voltage in saturation is given by Equation 14.

$$V_{DS} > R_{ON} \times I_{D} \tag{14}$$

During linear operation, the drain to source voltage is given by Equation 15

$$V_{DS} = R_{ON} \times I_{D} \tag{15}$$

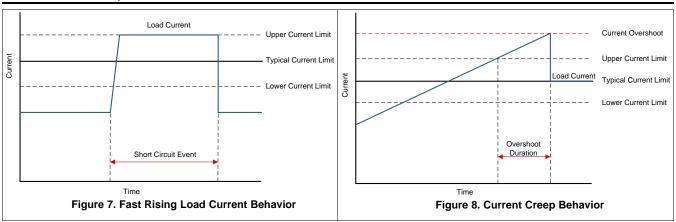

In this linear region, the current limit ratio is not defined by the datasheet. The current limit meets datasheet specifications only when the FET is saturated by a fast increment of load current such as short circuit events, capacitor charging and inrush current clamping. A slow current creep keeps the FET in its linear region longer, causing a loss of current limit accuracy. Figure 7 and Figure 8 describe the behavior of TPSxHxxx devices.

Current Limit Accuracy www.ti.com

Typical current limits during normal operation are bounded by an upper and a lower limit that is ±15% of the set value. When the load current is below the lower limit, the FET is in its linear region. As the load current increases slowly and reaches the upper limit, the FET stays in the linear region and causes the load current to overshoot the upper limit by as much as 25% at low temperatures before the sense FET reaches saturation. However, the devices include an extra trip mechanism that is shown as the current loop in Figure 9, which now clamps the load current. Figure 9 is similar to Figure 3, however it includes the sense FET circuit used in the extra current limit loop. The current limit ratio is then brought back into compliance with the specification on the datasheet.

Figure 9. TPSxHxxx Current Limit Mirror Circuitry

The closed loop amplifier  $OP_{SNS}$  regulates the current at the CL pin so that the inverting and the non inverting inputs have the same voltage. The voltage in the inverting input is given by Equation 16 where  $I_{SNS}$  is the sense FET drain current.

www.ti.com Current Limit Accuracy

$$V_{-} = V_{S} - (R_{S1} \times I_{SNS}) \tag{16}$$

The voltage at the non inverting input is given by Equation 17. Icl is the CL pin sourcing current.

$$V_{+} = V_{S} - (R_{S2} \times I_{CL})$$

(17)

Since the voltages at these inputs are held constant, Equation 18 describes the fixed relation irrespective of the FET being in linear or saturation regions.

$$R_{S1} \times I_{SNS} = R_{S2} \times I_{CL} \tag{18}$$

The relation between the drain to source voltages of the sense FET and the power FET is shown in Equation 19.

$$V_{DS, power} = V_{DS, sense} + (R_{S1} \times I_{SNS})$$

$$(19)$$

$$R_{\text{ON, power}} \times I_{\text{OUT}} = (R_{\text{ON, sense}} + R_{\text{S1}}) \times I_{\text{SNS}}$$

$$(20)$$

The ratio between the sense current and the load current in the linear region is given as Equation 21.

$$K_{\text{CL, actual}} = I_{\text{OUT}} \div I_{\text{SNS}} = (R_{\text{ON, sense}} + R_{\text{S1}}) \div R_{\text{ON, power}}$$

$$\tag{21}$$

The specified current ratio in the datasheet as  $K_{CL}$  is Equation 22 and describes the FET in the saturation region.

$$K_{CL} = (R_{ON, sense} \div R_{ON, power})$$

(22)

The offset between Equation 21 and Equation 22 is  $(R_{S1} \div R_{ON, power})$ . This results in the current ratio being higher than the given datasheet specification in the linear region. This increase in current ratio results in the loss of current limit accuracy during a slow load current ramp. This overshoot ends as soon as the FET hits its saturation region. It is not typically possible to calculate the exact value of this overshoot, however it temps to be in the range of 25% to 50% depending on operating temperature.

Equation 21 also states that the inaccuracies due to current creeping will be maximized at lower temperature operation because of the lower on resistance of the power FET integrated in the device. At normal to higher temperature operation, current creeping overshoots are still present but are lower than 25%. It is recommended that a design using TPSxHxxx devices has sufficient power budgeting and protection to withstand current creep during the overshoot duration.

For example, if the current limit is set at 1 A for a specific design, the upper current limit will be 1.15 A during an event such as short to ground, capacitor charging or inrush current clamping. During low temperature operation and if the current is creeping, the overshoot limit in this case will be 25% in excess of the upper limit resulting in a limit of 1.44 A. The load and the source must be rated for this current drawn. The overshoot duration is dependant on the rate at which the load current increases through the system. Hence, slow current creep should be avoided when working with sensitive loads.

## 4.2 TPSxHBxx Current Limiting

Three situations broadly describe the different faults that could occur in systems using TPSxHBxx switches:

- A slow incremental creep of the load current during the switching of inductive loads.

- A fast increment of the load current when the device is enabled into a short circuit.

- A fast increment of the load current by shorting the circuit during normal operation, or "hot short".

The version of the TPSxHBxx device dictates the behavior of the device after the fault is hit. All TPSxHBxx switches include a Version A and a Version B that result in immediate shutdown of the switch when the limit is hit.

During slow current creep, the device has enough time to respond to the fault and the current limit is triggered at the specified value in the datasheet. Figure 10 shows the immediate shutdown behavior of Version A or B devices. The sense voltage gradually ramps up following the load current. When the load current reaches the set current limit, the sense voltage is held at its fault voltage by sourcing the fault indication current I<sub>SNSFH</sub> from the SNS pin. This is done to differentiate between normal operation and fault operation of the switch.

Current Limit Accuracy www.ti.com

Figure 10. TPSxHBxx Slow Ramp Current Limiting ( $I_{LIM} = 7 A$ )

During an enable into a short circuit, the load current rises quickly and overshoots the set current limit for a few microseconds before the device can respond to the short. During turn on, the on resistance of the switch is higher than the steady state on resistance. This limits the current overshoot before the fault is triggered. The minimum short circuit duration is limited by turnon time t<sub>ON</sub> and fault indication time t<sub>FAULT</sub>. Figure 11 shows the behavior of version A or B of the TPSxHBxx devices in the event of enabling into a short circuit.

Figure 11. TPSxHBxx EN into Short Current Limiting ( $I_{LIM} = 7 A$ )

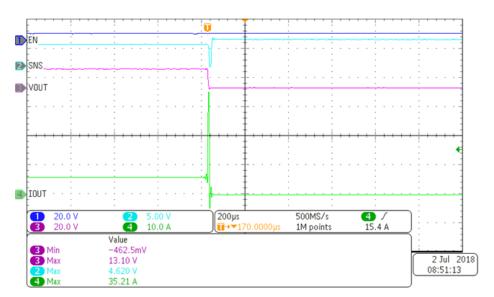

During a "hot short" event, where the device is already enabled and outputting current when the short circuit occurs, the load current once again spikes and causes an overshoot for a few microseconds. This overshoot is significantly higher than the enable into short event due to the low steady state on resistance of the device. Figure 12 shows the behavior of TPSxHBxx devices in the event of a hot short.

www.ti.com Current Limit Accuracy

Figure 12. TPSxHBxx Hot Short Current Clamping (I<sub>LIM</sub> = 7 A)

#### 4.2.1 Temperature Effects on TPSxHBxx Version B Internal Current Limit

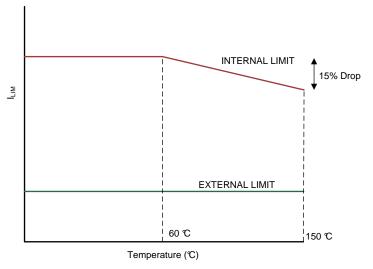

As discussed in Section 3.2, if the TPSxHBxx version B devices have an R<sub>ILIM</sub> that is shorted, missing, or out of range the device will revert to a fixed internal current limit. In this case the internal current limit reference folds back with higher operating temperature to mitigate damage that may occur to the device as well as to protect loads that are further downstream from high power dissipation. Figure 13 shows the drop of the internal current limit reference value. TPSxHxxx devices and versions A of the TPSxHBxx devices do not feature this fold back due to the lower load current specification.

Figure 13. TPSxHBxx Version B Internal Current Limit Foldback

Application Example www.ti.com

#### 5 Application Example

#### 5.1 Start-Up Inrush Current Clamping

As discussed in Section 2, current limit functionality is implemented in most Smart Power Switches available in the market, however, the limit threshold is generally fixed internally at a very high level due to the requirement to drive high wattage bulbs. For other loads, this threshold is too large to use for effective protection. In automotive infotainment systems, around  $100~\text{m}\Omega~R_{\text{ON}}$  devices are used to drive a display module in which the nominal current is only 1 A but with a load that includes a  $1000~\mu\text{F}$  input capacitor. If a conventional Power Switch is used, the larger fixed current limit cannot protect from inrush current up to 15 A. This creates a cost concern for system design since the parts, PCB traces and external wires all need to have the right tolerances and gauge to withstand the high inrush current, but then are over specified for the low operating currents. To address the inrush current challenge, Texas Instruments introduces the adjustable current limit function in the new Smart Power Switch family. For a more detailed analysis of this application case, please reference Tl's Driving Capacitive, Inductive, and LED lightning app note.

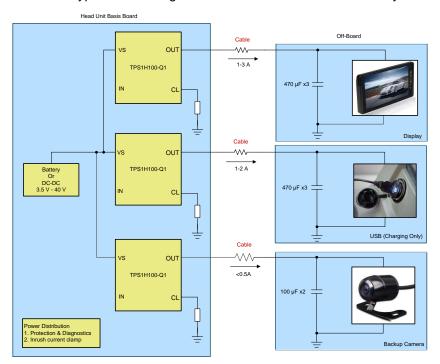

These devices are suitable as a start-up inrush current clamp, especially when driving a capacitive load. Figure 14 again shows a typical block diagram in the automotive infotainment system.

Figure 14. Using Smart Power Switch as Inrush Current Clamper in Infotainment System

With the adjustable current limit function, these devices can clamp the inrush current to the user defined value. This saves the designer system level costs by minimizing trace widths, board weight, wire gauge size and component tolerances.

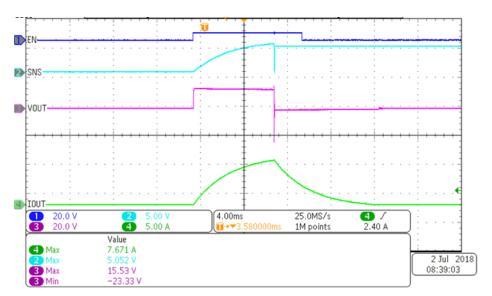

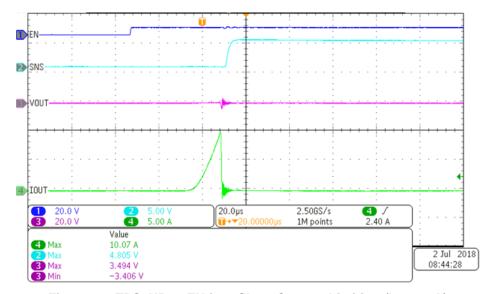

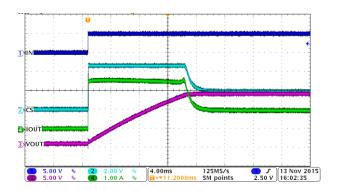

Figure 15 and Figure 16 use the TPS1H100-Q1 at a  $V_s$  = 13.5 V and  $I_{OUT}$  = 1 A. The output loads are 5 units of 470  $\mu$ F electrolytic capacitors in parallel to simulate an automotive infotainment system. The current limit threshold is set at 2.5 A. They show the inrush event on enable.

Figure 15 shows a zoomed-out waveform under 85°C ambient temperature. No thermal shutdowns are triggered during the charging cycle.

www.ti.com Application Example

Figure 15. Zoomed-Out Waveform of Inrush Clamping

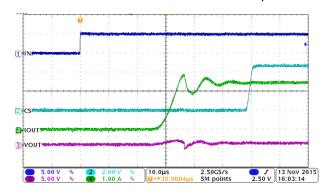

Figure 16 shows a zoomed-in waveform under 85°C ambient temperature.

Figure 16. Zoomed-In Waveform of Inrush Clamping

## 5.2 Fast-Trip Response for Short Circuit Events

Short circuit events are common failures and can lead to load damage if not protected against. In addition to the inrush current during start-up (Section 5.1), the hard short (IN is active, output cable short to GND, shown as Figure 17) is a failure that the Smart Power Switch protects against. This fault was discussed briefly in Section 2, but is discussed in greater depth here.

Figure 17. Hard Short

For better protection from the hard short, the device implements a fast-trip protection to turn off the channel immediately (response time <1  $\mu$ s) ahead of current limit loop. Figure 18 shows the fast trip implementation and is similar to Figure 3 with a focus on the fast-trip circuitry.

Application Example www.ti.com

Figure 18. Internal Block Diagram of Hard Short Implementation

With the fast response, the device can achieve better overshoot current suppression performance.

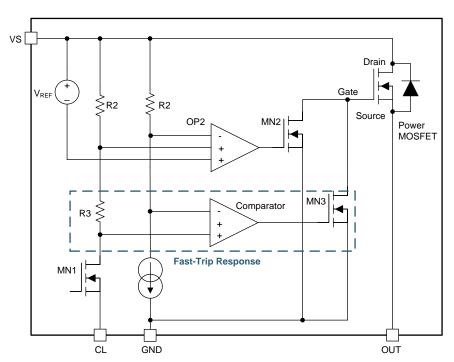

Figure 19 uses the TPS1H100-Q1 at a supply  $V_S = 13.5$  V. IN is active and the current limit value is set to 1 A. A hard short happens with a cable (5  $\mu$ H + 100 m $\Omega$ , according to AEC Q100-012 standard).

Figure 19. Hard Short Current Waveform

The fast-trip response suppresses the high inrush current to protect the switch and the load before the current limit loop can clamp the load current. Section 4.2 describes the various faults that can occur and device response to each fault in detail.

www.ti.com Application Example

#### 5.3 Smart LED Driver

With the trend of replacing incandescent and halogen lamps with LEDs, the high side driver topology is popular in the market. This topology has both the short-to-GND protection and common-cathode connection advantages.

Because LED's are generally low current loads, it is ideal to set a very low current limit for LED load driving so these applications benefit from the adjustable current limit function. For more details on driving LED's with TI Smart Power Switches, reference the LED driving section of TI's Driving Capacitive, Inductive, and LED lightning app note.

#### 5.4 Dynamic Inrush Current Control

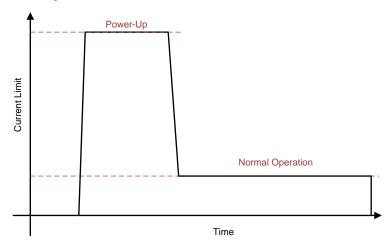

During turn on, some loads can pull a large inrush current if they are capacitive in nature. Automotive incandescent bulbs require >10 times the nominal current for a fast turn-on, and for some inductive loads (solenoid, relay and motor), around 2-6 times the nominal current is needed. After power up, a lower current limit is needed for better protection, especially if a short to GND occurs. This dynamic limit functionality is shown in Figure 20.

Figure 20. Dynamic Current Limit Control

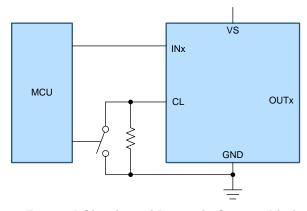

With some additional external circuitry, the Smart Power Switches can meet this dynamic current limit need. Figure 21 shows one recommended connection involving a resistor and a short shunt between the CL pin and GND. When powering up, MCU shorts the CL pin to GND thus setting the higher internal current limit as the reference. After the turn on period, the MCU then disconnects the short to set the lower external current limit as the reference.

Figure 21. External Circuitry of Dynamic Current Limit Control

Summary www.ti.com

## 6 Summary

Smart Power Switches are devices with protection and diagnosis features which benefit system design by featuring intelligent fault detection with high reliability. They are widely used in automotive and industrial applications.

Common design issues for such applications are overload currents and various short circuit events. To address these issues, Texas Instruments offers a wide range of Smart Power Switches with differing on resistance, number of channels and adjustable current limits. They provides solutions to common challenges for low power and high power designs. These devices improve the reliability of the whole design by increasing efficiency and adding adjustable protection against high current draw events while reducing system level costs.

www.ti.com Revision History

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from A Revision (July 2018) to B Revision |                                                                             |      |

|---------------------------------------------------|-----------------------------------------------------------------------------|------|

| •                                                 | Added Section 2 section  Revised Section 3.1.  Updated Table 2 and Table 3. | 5    |

| Ch                                                | nanges from Original (November 2016) to A Revision                          | Page |

| •                                                 | Updates were made in Abstract                                               | 1    |

| •                                                 | Updates were made in Section 1                                              | 3    |

| •                                                 | Added information about versions                                            | 3    |

| •                                                 | Added information about low on resistance                                   | 3    |

| •                                                 | Updates were made in Section 2.1                                            | 5    |

| •                                                 | Added Section 2.2                                                           | 7    |

| •                                                 | Changed Section 2.2 to Section 3.1 and Updated                              | 8    |

| •                                                 | Added Section 3.2                                                           | g    |

| •                                                 | Added Section 3.4                                                           | 11   |

| •                                                 | Added Section 3.3                                                           | 13   |

| •                                                 | Changed Section 3.1 to Section 4.1 and Updated                              |      |

| •                                                 | Changed Section 3.2 to Section 4.2 and Updated                              |      |

| •                                                 | Changed Section 3.3 to Section 4.3 and Updated                              |      |

| •                                                 | Changed Section 3.4 to Section 4.4 and Updated                              |      |

| •                                                 | Changed Section 4 to Section 5 and Updated                                  | 18   |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated