# Interfacing the ADS786x to TMS470 Processors

Tom Hendrick

Data Acquisition Products

#### **ABSTRACT**

This application report presents methods of interfacing the ADS7866/67/68 12/10/8-bit SAR analog-to-digital converter to the serial peripheral interface (SPI) port of the TMS470 processors. The flexible clocking scheme of the TMS470 SPI port, along with its internal 16-bit shift register provides an easy hardware/software interface to this series of high-speed, micro power SAR converters. Project collateral discussed in this application report can be downloaded from the following URL: www.ti.com/lit/zip/SLAA312.

# Contents

| 1 | Introduction                     | - 1 |

|---|----------------------------------|-----|

| 2 | Hardware                         | 1   |

| 3 | Software Interface               | 2   |

| 4 | Power and Performance            |     |

| 5 | Conclusion                       | 2   |

| 6 | References                       | 4   |

|   | List of Figures                  |     |

| 1 | Hardware Interface Block Diagram |     |

| 2 | Complete Conversion Cycle        | 3   |

|   | List of Tables                   |     |

| 1 | Cable Requirements               | 2   |

|   |                                  |     |

#### **Trademarks**

Embedded Workbench is a trademark of IAR Systems.

## 1 Introduction

The ADS7866, ADS7867, and ADS7868 are low-power, miniature, 12/10/8-bit A/D converters, each with a unipolar, single-ended input. These devices can operate from a single 1.6-V to 3.6-V supply with a 200-to-280 KSPS throughput rate. This series of ADCs can maintain at least a 100-KSPS throughput with a supply as low as 1.2 V, making them ideal candidates for low-power applications requiring high-speed data acquisition.

TMS470 devices, such as the TMS470R1B1M, can be used in a simple and straight-forward interface that requires no *glue logic* and little software overhead.

## 2 Hardware

The hardware used to produce the timing diagrams found throughout this application report includes the TMS470R1B1M Kickstart Development Kit and the ADS7866/67/68 evaluation module (EVM).

Hardware www.ti.com

#### 2.1 ADS6766/67/68EVM

The ADS7866/67/68EVM is a member of the modular EVM series of serial ADCs available from Texas Instruments. The EVM provides a platform to demonstrate the functionality of the ADS7866, ADS7867, or ADS7868 ADC with various Texas Instruments DSPs and microcontrollers, while allowing easy access to all analog and digital signals for customized end-user applications. For more information on the EVM, see the TI user's guide SLAU181.

# 2.2 TMS470R1B1M Kickstart Development Kit

The TMDS-FET470R1B1M is a complete development kit including all the hardware and software necessary to evaluate the TMS470R1B1M microcontroller. The hardware is provided in a convenient modular form factor. The TMDS-FET470R1B1M uses the IAR Embedded Workbench™ Integrated Development Environment (IDE) to provide full emulation with the option of designing with a stand-alone system or detaching the removable target board for integration with external analog components via the HPA-MCU Interface Board (SLAU106).

#### 2.3 Hardware Interface

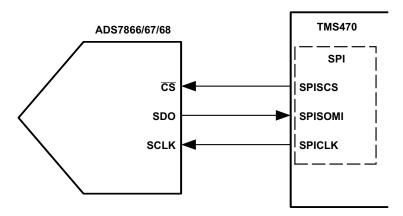

A simple three-wire interface is the minimum requirement to connect the TMDS-FET470R1B1M and the ADS7866/67/68EVM. The hardware connections are shown in Figure 1. The Serial Clock (SCLK), Chip Select (CS), and Serial Data Output (SDO) pins from the ADC are connected to SPI Clock (SPICLK), SPI Slave Chip Select (SPISCS), and SPI Slave Out Master In (SPISOMI) pins, respectively, of the SPI port. For this application report, the first SPI port (SPI1) was used.

Figure 1. Hardware Interface Block Diagram

**Table 1. Cable Requirements**

| ADS7866/67/68 EVM          | TMS470R1AM Carrier Board |

|----------------------------|--------------------------|

| J2.1 or J2.7 – Chip Select | SPI1SCS                  |

| J2.3 – CLOCK               | SPI1CLK                  |

| J2.13 – Data Out           | SPI1SOMI                 |

#### 3 Software Interface

All the software was written and compiled using the Kickstart version of Embedded Workbench™ from IAR. This software is the free version of the IDE and is available for download from the TI Web site. The code used in these examples is available on request.

www.ti.com Software Interface

## 3.1 SPI1 Settings

SPI Control registers 1 and 2 (SPICTRL1 and SPICTRL2) set up the basic operation of the serial interface. Character length and clock speed are set in SPICTL1 by writing 0x230 to the register. This sets up the port for 16-bit transfers with a serial clock of 3.3 MHz. The port is configured in SPI master mode with CPOL=1 and CPHA=0 by writing 0x2A to the SPICTRL2 register.

The SPISOMI, SPICLK, and SPISCS functions are enabled in the SPI Pin Control register 6 (SPIPC6) by writing 0x1E to the SPIPC6 register. The output pin, SPISIMO, also is enabled in this step. This pin could be used to drive the input to an SPI-based DAC if desired.

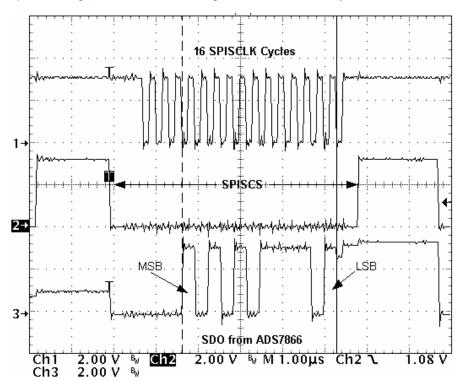

By setting the CHARLEN bits in the SPICTRL to 0x10, 16 serial clocks are transmitted from the TMS470 to the ADS7866/67/68 on each conversion cycle. The serial shift register is automatically set to act as a 16-bit transmit/receive buffer. Transmitted data is MSB aligned and commences with the first SCLK cycle.

## 3.2 Starting a Conversion

By connecting the SPISCS output of the SPI port to the  $\overline{\text{CS}}$  input on the ADS7866/67/68 EVM, a conversion cycle is started when data is written to the SPI Data register (SPIDAT). The SPISCS is driven low by the TMS470 before the commencement of the serial data clock.

The  $\overline{\text{CS}}$  pin also can be controlled by GPIO. In cases where a single SPI port is driving multiple devices, using GPIO to control individual Chip Select lines allows the user to share common SPICLK, SPISOMI, and SPISIMO lines.

The ADC begins to output the conversion results (MSB first) on the fourth SCLK cycle after the  $\overline{\text{CS}}$  pin toggles. Because the shift register holds the last 16-bits of received data, the entire conversion result is captured for further processing. Shifting the received data right by 1 bit provides proper LSB alignment. The scope capture of Figure 2 shows the timing of one conversion cycle.

Figure 2. Complete Conversion Cycle

Power and Performance www.ti.com

## 4 Power and Performance

The combining of the low-power and high-performance ADS7866, ADS7867, and ADS7868 with the SPI port of TMS470 processors is a relatively simple and straight forward task. System performance characteristics of 71-dB SNR, –83-dB THD, and ±1.5-LSB linearity are possible using little power.

For this application report, the ADS7866EVM was powered at 3.3 V, allowing direct connections between the device and the TMS470 controller, without any additional glue logic. The ADC sample rate was approximately 130 kSPS using a 3.3-MHz clock. Total current drawn from the ADC supply was approximately 323  $\mu$ A.

## 5 Conclusion

The low-power and high-performance ADS7866, ADS7867, and ADS7868 combined with the SPI port of TMS470 processors is a relatively simple and straight-forward task. In low-power or battery applications requiring high-performance data acquisition, the combination of the TMS470 and ultralow power ADCs from Texas Instruments provides a perfect combination of price and performance.

#### 6 References

- 1. ADS7866/67/68 1.2-V, 12-/10-/8-Bit, 200-KSPS/100-KSPS, Micro-Power, Miniature Analog-to-Digital Converter With Serial Interface data sheet (SLAS465)

- 2. TMS470R1x Serial Peripheral Interface (SPI) Reference Guide (SPNU195)

- 3. HPA-MCU Interface Board User's Guide (SLAU106)

- 4. ADS7866/67/68EVM User's Guide (SLAU181)

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated